FPGA验证流程(远程实验版)

在线代码编辑与云编译

前面的环节应已经完成电路设计,并且用Quartus软件编译生成了电路文件,则可以跳过这一步,直接进入实验验证流程。 如果尚未完成代码编辑与编译,这里介绍远程实验平台提供的在线代码编辑和云端编译器。

从实验界面工具条上的任务列表中选择“代码与编译”,会自动打开在线代码编辑器,其中已经定义了一个VirtualBoard模块,可以看到该模块只有端口声明,如例 1所示。

`default_nettype none

module VirtualBoard (

input wire CLOCK, // 10 MHz Input Clock

input wire [19:0] PB, // 20 Push Buttons, logical 1 when pressed

input wire [35:0] S, // 36 Switches

output logic [35:0] L, // 36 LEDs, drive logical 1 to light up

output logic [7:0] SD7, // 8 common anode Seven-segment Display

output logic [7:0] SD6,

output logic [7:0] SD5,

output logic [7:0] SD4,

output logic [7:0] SD3,

output logic [7:0] SD2,

output logic [7:0] SD1,

output logic [7:0] SD0

);

endmodule例 1的VHDL版本(点击此行展开)

如果希望用VHDL,可以用下面VHDL版本的虚拟实验板模块覆盖在线代码编辑器中的代码。

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY VirtualBoard IS

PORT (

CLOCK:in std_logic; -- 10MHz Input Clock

PB: in std_logic_vector(19 downto 0); -- 20 Push buttons, logical 1 when pressed

S: in std_logic_vector(35 downto 0); -- 36 Switches

L: out std_logic_vector(35 downto 0); -- 36 LEDs, drive logical 1 to light up

SD7:out std_logic_vector(7 downto 0); -- 8 common anode Seven-segment Display

SD6:out std_logic_vector(7 downto 0);

SD5:out std_logic_vector(7 downto 0);

SD4:out std_logic_vector(7 downto 0);

SD3:out std_logic_vector(7 downto 0);

SD2:out std_logic_vector(7 downto 0);

SD1:out std_logic_vector(7 downto 0);

SD0:out std_logic_vector(7 downto 0));

END VirtualBoard;

ARCHITECTURE behav_VB OF VirtualBoard IS

BEGIN

END behav_VB;这个VirtualBoard模块可以想象成一个实验板,有1个时钟输入CLOCK, 20个按键PB0~PB19,36个拨动开关S0~S35,36个指示灯L0~L35,8个七段数码管SD0~SD7。该模块命名为“VirtualBoard”的含义是“虚拟实验板”,在后面验证时我们会看到,“虚拟实验板”模块与实验调试软件的“虚拟面板”是相互对应的。

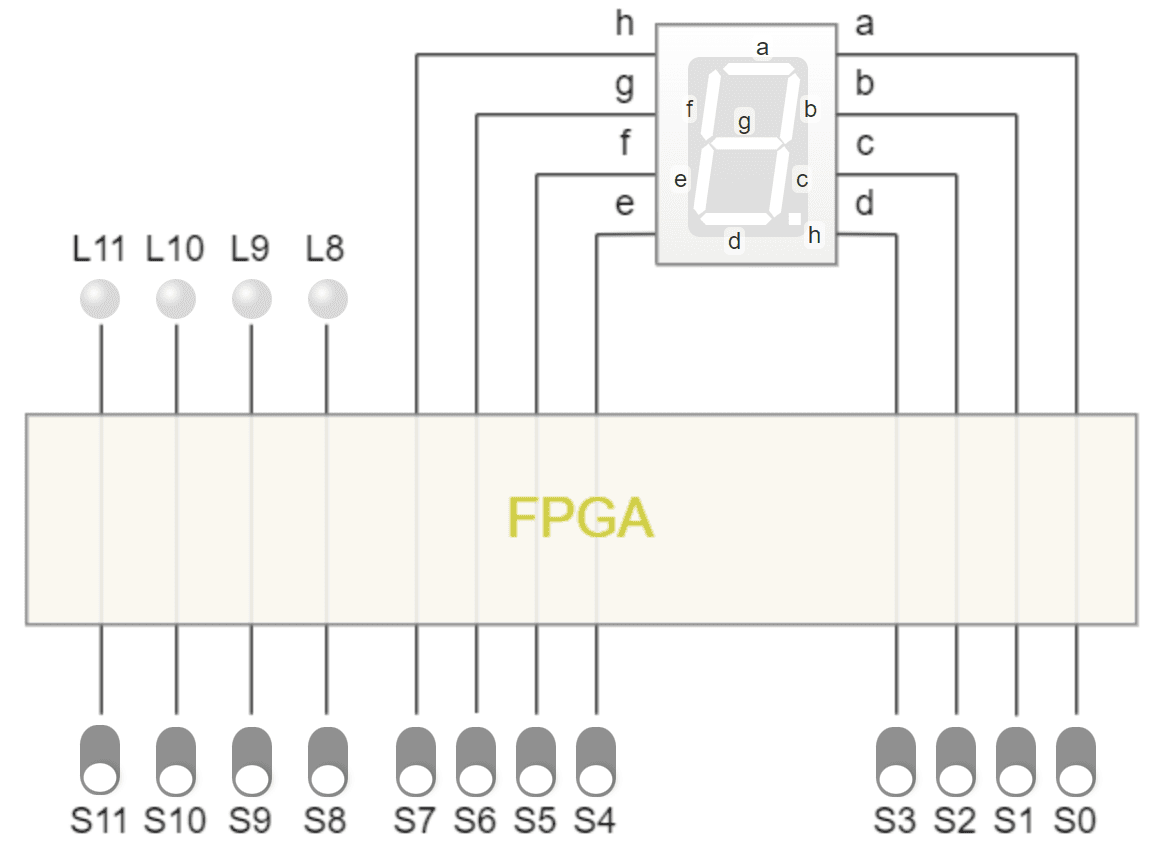

下面为VirtualBoard模块添加设计代码,如例 2所示。语句①用8个拨动开关S7~S0直接驱动七段数码管SD0的8个段;语句②需要自己编写,用S11~S8控制L11~L8的亮灭;语句③用按键PB0驱动指示灯L18。将例 2的代码添加到例 1的 endmodule 之前。

//开关7~0直接驱动数码管SD0的各个段

assign SD0 = S[7:0]; (1)

//开关11~8驱动指示灯L11~8的亮灭

(2)

//按键PB0驱动指示灯L18

assign L[18] = PB[0]; (3)例 2的VHDL版本(点击此行展开)

--开关7~0直接驱动数码管SD0的各个段 SD0 <= S(7 downto 0); (1) --开关11~8驱动指示灯L11~8的亮灭 (2) --按键PB0驱动指示灯L18 L(18) <= PB(0); (3)

点击“编译”按钮,云端服务器将对编辑器中的代码进行远程编译。

实验验证流程

选择验证任务

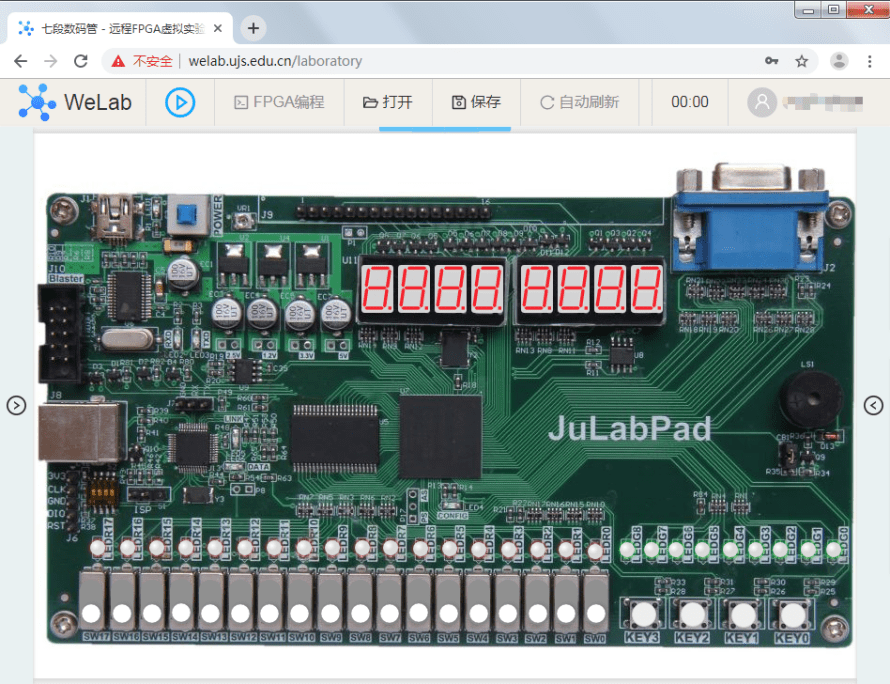

选择任务列表中的“虚拟实验板”,打开虚拟面板界面,如图 2,这个虚拟面板以实验板的实物照片为背景,在开关、指示灯等输入输出元件位置上放置了虚拟元件。

| 实验材料中提供的虚拟实验板.jvp与图 2虚拟面板相同,用于本地实验软件;远程实验平台自动从后台加载虚拟面板,无需手动打开。当然,远程实验平台与本地实验软件的虚拟面板文件可互换,所以也可通过工具条上的“打开”按钮加载该文件。 |

加载FPGA电路

开始验证之前首先要将编译生成的FPGA电路文件加载到FPGA芯片中(也称配置、编程)。点击“FPGA编程”,在打开的文件对话框中选择云编译生成的xxx.rbf文件;如果是之前“FPGA 设计流程”实验中本地Quartus编译的,这里选择“本地上传”。编程过程中会出现进度指示,完成后会有提示“文件加载完成”。

认识虚拟元件

将鼠标指针指向某个虚拟元件,会提示该元件的名称和当前状态,这些虚拟元件的名称与VirtualBoard模块的端口名称相对应,见例 1端口名称的注释。下面通过操作虚拟面板了解虚拟元件的特性。

-

虚拟拨动开关

初始状态开关的颜色是灰色的,用鼠标指向最右边的开关,提示“S0:低电平”,表明该开关的状态是低电平;点击开关,开关的颜色变为蓝色,提示“S0:高电平”。

-

虚拟LED指示灯

点击虚拟开关S8,使其产生高电平,指示灯L8应点亮。同样地,S9~S11为高电平时,指示灯L9~L11应点亮。如果与预期不同,检查例 2语句②是否正确。

-

虚拟数码管

根据例 2语句①,S0~S7驱动数码管SD0。点击虚拟开关S0~S7,虚拟面板中最右边的数码管SD0显示内容应有变化。可以看出,点亮电平与指示灯不同,数码管是低电平点亮的。观察S0~S7与数码管字段的对应关系,可知S0~S7对应段a~段h。

-

虚拟按键

根据例 2语句③,按键PB0驱动指示灯L18。但是点击PB0,L18却没有任何反应;延长按下的时间,仍然没有反应。根据代码中PB端口的注释,按键按下时输出“1”,为什么L18没有点亮呢?这是因为远程实验软件做了一个特殊处理,按键按下时前端浏览器并没有向后端发消息,当按键松开时才向后端服务器发送“按键动作”的消息;后端服务器收到这个消息后,先使PB0为1,随即使PB0为0,也就是按键按下又松开的动作;之后再采集指示灯的状态返回给前端,此时指示灯已经回到“0”的状态,所以浏览器界面看不出任何变化。在后面的实验中,按键的主要用途是产生一个正脉冲。如果需要产生稳定的电平,应使用拨动开关。这一点和本地实验系统不同,在本地实验中,按下PB0不松开,能看到L18点亮,松开后L18熄灭。这是因为本地实验系统通过USB连接实验板,实验软件能够将鼠标点击的按下、松开两个动作实时地传递给实验板。

设计虚拟面板

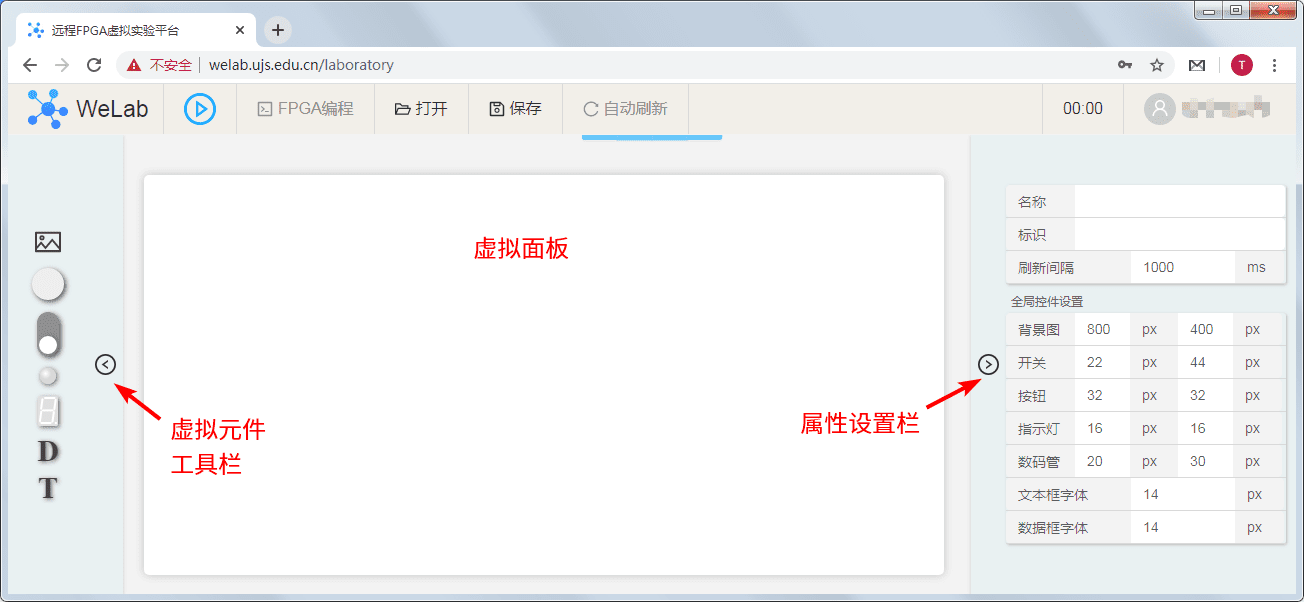

下面从头设计一个全新的虚拟面板。在任务列表中选择“设计虚拟面板并记录验证”,出现一个空白的虚拟面板,如图 3,可以自己添加背景图形和元件。

绘制面板背景图

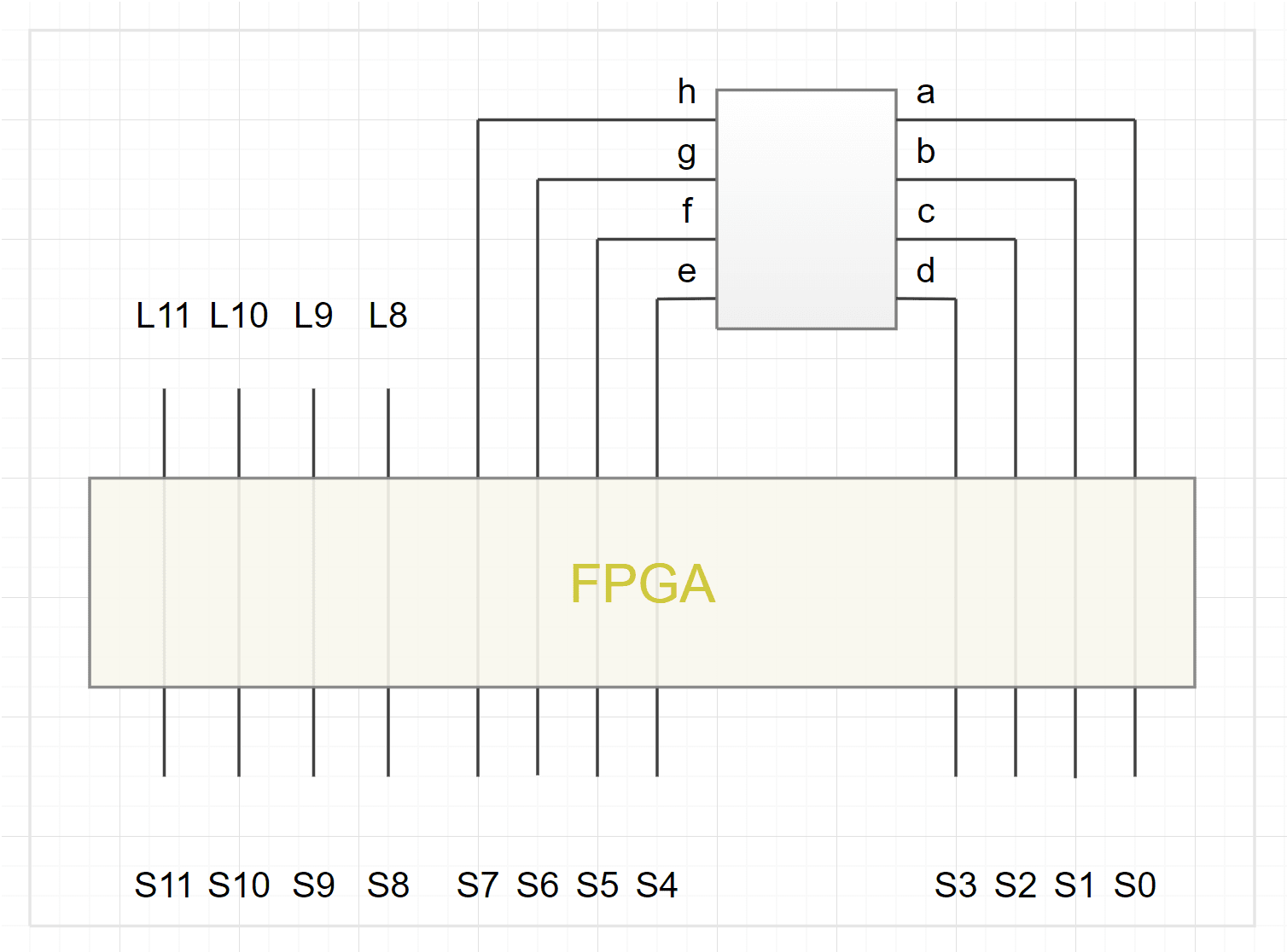

背景图展示虚拟元件之间的连接关系,有助于实验过程中分析实验结果。可使用自己熟悉的绘图软件绘制背景图,这里推荐开源软件diagrams.net(又名draw.io)。diagrams.net有Web版和桌面版, 可从https://www.diagrams.net进入Web版或下载桌面版。

绘制完成的效果如图 4。

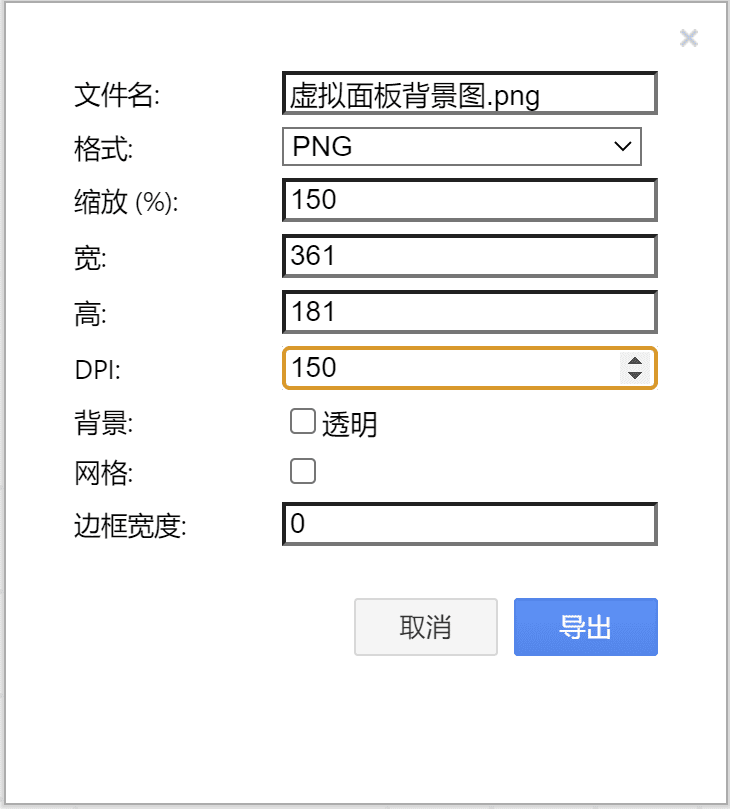

如果暂时不打算自己绘图,实验材料中提供了已绘制完成的文件“虚拟面板背景图.drawio”,只需导出为图像格式即可。 点击菜单“文件 ➤ 导出为 ➤ 高级…”,格式选择PNG,DPI设置为150,如图 5。

实验材料中也提供了一个导出的“虚拟面板背景图.png”文件,可直接使用。

添加背景图

在空白虚拟面板左边的虚拟元件工具栏中点击最上边的图片按钮,选择图片文件作为虚拟面板背景图。实验平台默认以图片尺寸作为虚拟面板的初始大小。

| 背景图的文件大小不宜过大,否则会影响虚拟面板的加载速度,超过1MB实验平台无法加载。 |

添加虚拟元件

现在我们给虚拟面板添加虚拟元件。以虚拟开关为例,从左边栏用鼠标左键点击并拖动开关图标![]() ,将开关图标拖到背景图上所希望的位置,然后松开鼠标左键将开关图标放置在虚拟面板上,此时右边栏显示了该开关的属性,第1个开关元件的序号是S0。放置元件时元件的序号是自动分配的,可以在右边属性栏的“序号”中手动进行修改。虚拟元件的名称和序号代表了设计代码中VirtualBoard模块的端口信号,如虚拟元件S0就是设计代码中的端口S[0]。

,将开关图标拖到背景图上所希望的位置,然后松开鼠标左键将开关图标放置在虚拟面板上,此时右边栏显示了该开关的属性,第1个开关元件的序号是S0。放置元件时元件的序号是自动分配的,可以在右边属性栏的“序号”中手动进行修改。虚拟元件的名称和序号代表了设计代码中VirtualBoard模块的端口信号,如虚拟元件S0就是设计代码中的端口S[0]。

用类似的方法添加需要的开关、数码管和指示灯。如果元件的排列不是很整齐,可以在选中元件后用键盘上的↑、↓、←、→键进行移动,也可以在右边属性栏的“位置”属性中输入精确的坐标值。元件的大小也可以通过右边属性栏修改,例如将指示灯的大小设置为20×20。除基本的位置、大小属性外,还可以通过属性设置开关的方向和指示灯的颜色。最终完成虚拟面板效果如图 6,其中段的名称“a, b, c…”使用了文本框元件(左边栏的图标“T”),该元件和电路没有关联,只是用于虚拟面板的标注。

实验考核

实验平台支持两种考核方式:验证记录和电路测试。

记录验证过程

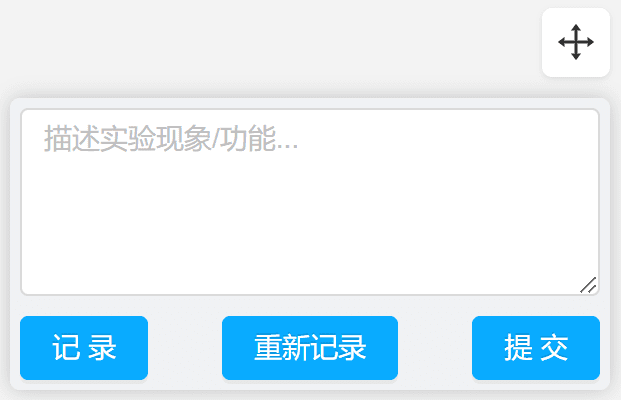

如果该实验任务有考核要求,虚拟面板界面上会出现用于记录验证过程的悬浮窗口,如图 7。如果不要求记录验证过程,悬浮窗中不出现“记录”按钮,或者不出现悬浮窗。(注:提交日期截止后,悬浮窗也不会出现。)

该功能可以理解为线下实验的教师现场检查场景,通过验证记录可以反映实验者对电路功能的理解,直观展示实验结果;教师通过回放功能评阅学生的验证记录。

本实验要求理解数码管的驱动原理,推断数码管是共阳极还是共阴极,找出数码管段编码与字形的对应关系。根据开关拨向0点亮还是拨向1点亮的实验现象,可以得出数码管是共阴极还是共阳极的结论;通过改变开关状态可以使数码管显示0~F十六个数字,找出所显示数字的七段编码并记录下来,在以后的七段译码器实验中将会用到这些编码。

记录窗口还提供了文字输入功能,用于分析实验现象、得出结论。是否要求输入文字描述由指导教师根据每个实验的特点决定。

特别提醒,每按下一次 记录 按钮,仅产生一条记录,后续的操作并不会自动地记录。也就是说,每一个需要回放的步骤都应该按下一次 记录 按钮。如果要对当前实验电路现象输入文字分析,也要在按下 记录 按钮之前输入。

|

重新记录 按钮按下后,会清空前面输入的所有记录,系统给出“记录已清空”的提示。 提交 按钮按下后,提交所有记录,实验板收回,系统提示“提交成功”和“本次实验已结束”。如果之后再次记录并提交,将覆盖之前提交的验证记录,并非追加在上次提交的记录后面。

验证记录提交以后,任务列表上会出现回放按钮![]() ,点击回放按钮可以观看自己的记录,确认操作没有遗漏。教师评分之后,才可以在回放界面右上角看到验证记录的成绩,如图 8。

,点击回放按钮可以观看自己的记录,确认操作没有遗漏。教师评分之后,才可以在回放界面右上角看到验证记录的成绩,如图 8。

| 提交后任务列表上该任务会显示“无需考核”,是指该任务不包含“电路测试”的考核,并非不考核验证记录。 |

小结

通过这个实验主要熟悉了开关、按键、指示灯、数码管等虚拟元件的特性,也初步了解了远程实验平台的使用,还有很多细节功能需要读者自己探索,也可观看由前端开发同学余乐韬制作的WeLab远程FPGA实验平台介绍视频,由于制作的时间较早,没有反映后来开发的考核等功能。

有关CPU实验的界面和使用,将在本书后面的CPU部分介绍。