RISC-V微架构实验

本实验是选做实验。

实验内容和要求

熟悉实验平台CPU实验界面

观看辅导视频,熟悉远程实验平台CPU实验界面的使用,如:向指令存储器中输入机器指令和注释,向数据存储器中输入数据,复位实验CPU电路,单步运行实验CPU,查看数据存储器的内容,导出、导入指令存储器内容。

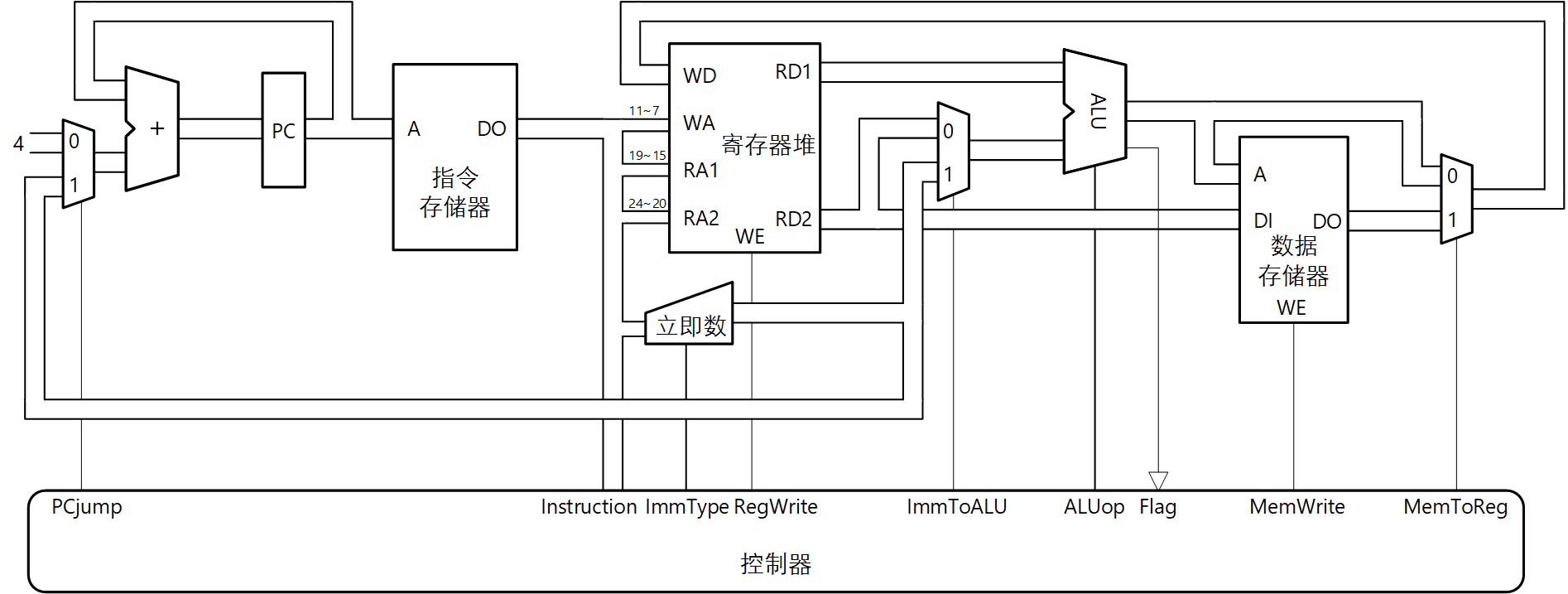

单周期微架构的RISC-V指令执行

实验材料中提供了单周期RISC-V的电路文件,它支持23条指令(见附录),包括R型和I型整数运算指令、存储器访问指令和分支指令,对应的微架构如图 1所示。将该电路文件加载到实验平台(注:远程实验平台从云端自动加载,无需实验材料中的电路文件),在指令存储器输入自己编写的RISC-V指令,单步执行并分析运行结果,如:控制器产生的控制信号,绿色高亮的信息流,数据通路上的数据值。

将前面实验用模拟器运行过的计算斐波那契数列的程序改写后在单周期微架构的RISC-V上运行。说明两点:

(1)受FPGA片内存储资源的限制,指令存储器的容量是512个字(2K字节),数据存储器的容量是64个字(256字节),大于255的数据存储器地址将被映射到0~255。例如,汇编语言程序中的.data起始地址为0x10000000,映射到硬件存储器的地址是0。

(2) 本实验的CPU硬件只能执行附录列出的指令,支持更多指令的微架构留作以后的设计任务。例如,该CPU不支持lui指令,“lui x3, 0x10000”可以用下面的两条语句代替。

addi x3, x0, 0x100 slli x3, x3, 20

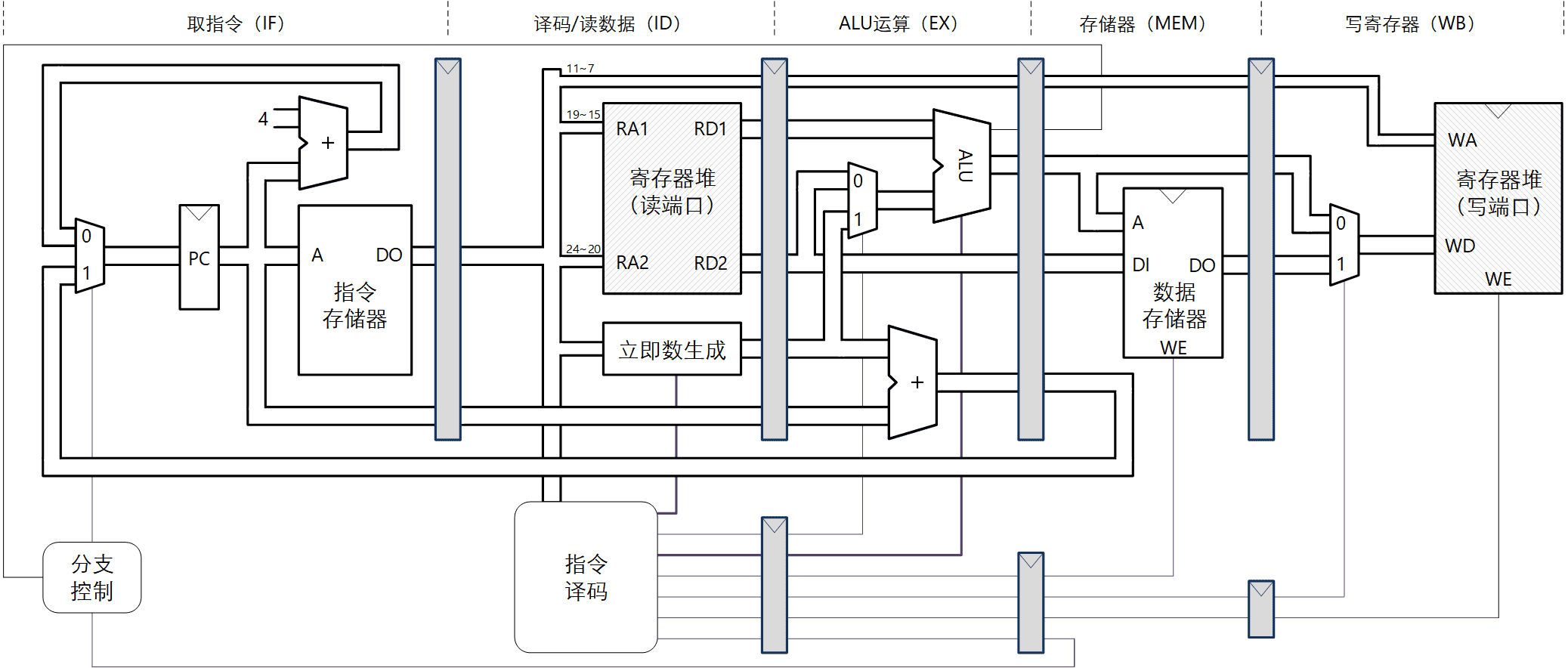

流水线微架构的RISC-V指令执行

实验材料中提供了流水线RISC-V的电路文件,它支持整数运算指令、存储器访问指令和分支指令,对应的微架构如图 2流水线微架构所示。(注:远程实验平台从云端自动加载电路文件,无需实验材料)

在流水线微架构上执行计算斐波那契数列的程序。如果发生数据冲突或控制冲突,用静态指令调度(调整指令顺序和插入空操作指令)的方法解决。根据你的实验结果,计算斐波那契数列的前6个数,在单周期微架构上需要多少个周期?在流水线微架构上需要多少个周期?假设流水线的时钟周期为T,单周期微架构的时钟周期为5T,你的程序在流水线执行的加速比是多少?要求写出计算依据。

附录 本实验CPU支持的指令

| 类别 | 指令名称 | 指令格式 | 汇编格式 |

|---|---|---|---|

整数运算 |

ADDI |

I |

addi rd,rs1,imm |

ADD |

R |

add rd,rs1,rs2 |

|

SUB |

R |

sub rd,rs1,rs2 |

|

AND |

R |

and rd,rs1,rs2 |

|

OR |

R |

or rd,rs1,rs2 |

|

XOR |

R |

xor rd,rs1,rs2 |

|

SLL |

R |

sll rd,rs1,rs2 |

|

SRL |

R |

srl rd,rs1,rs2 |

|

SRA |

R |

sra rd,rs1,rs2 |

|

ANDI |

I |

andi rd,rs1,imm |

|

ORI |

I |

ori rd,rs1,imm |

|

XORI |

I |

xori rd,rs1,imm |

|

SLLI |

I |

slli rd,rs1,3 |

|

SRLI |

I |

srli rd,rs1,3 |

|

SRAI |

I |

srai rd,rs1,3 |

|

访存 |

LW |

I |

lw rd,imm(rs1) |

SW |

S |

sw rd,imm(rs1) |

|

分支 |

BEQ |

B |

beq rd,rs1,imm |

BNE |

B |

bne rd,rs1,imm |

|

BLT |

B |

blt rd,rs1,imm |

|

BGE |

B |

bge rd,rs1,imm |

|

BLTU |

B |

bltu rd,rs1,imm |

|

BGEU |

B |

bgeu rd,rs1,imm |