三态门和多路器实验

参考设计:三态门

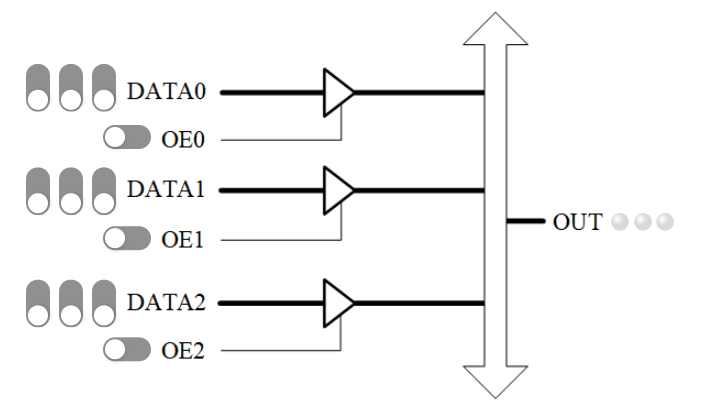

实验原理图如图 1。

例 1给出了图 1电路的Verilog设计。VirtualBoard模块的端口在实验环境的代码框架中已经介绍过,在以后的示例代码中,为节省篇幅,将不再重复端口声明部分。 模块的主体代码分为三个部分。第一部分将输入端口替换为一些内部信号,这些内部信号的命名与图 1原理图中的符号对应,目的是使代码更易读。第二部分是逻辑设计,这里用条件表达式描述了三态逻辑,输出信号的名称也是采用了与原理图一致的符号,在第三部分将这些输出信号赋给LED指示灯的输出端口。

`default_nettype none

module VirtualBoard (

input wire CLOCK, // 10 MHz Input Clock

input wire [19:0] PB, // 20 Push Buttons, logical 1 when pressed

input wire [35:0] S, // 36 Switches

output logic [35:0] L, // 36 LEDs, drive logical 1 to light up

output logic [7:0] SD7, // 8 common anode Seven-segment Display

output logic [7:0] SD6,

output logic [7:0] SD5,

output logic [7:0] SD4,

output logic [7:0] SD3,

output logic [7:0] SD2,

output logic [7:0] SD1,

output logic [7:0] SD0

);

/****** Replace input ports with internal signals *******/

wire [2:0] data0 = S[2:0];

wire [2:0] data1 = S[5:3];

wire [2:0] data2 = S[8:6];

wire oe0 = S[9];

wire oe1 = S[10];

wire oe2 = S[11];

/************* The logic of this experiment *************/

wire [2:0] out;

assign out = oe0 ? data0 : 3'bzzz;

assign out = oe1 ? data1 : 3'bzzz;

assign out = oe2 ? data2 : 3'bzzz;

/***** Internal signals assignment to output ports ******/

assign L[2:0] = out;

endmodule读懂代码后用实验系统验证,通过验证理解三态门的特性和正确用法。考虑以下问题,并通过实验找出答案。

(1)如果有2个或2个以上的三态门同时打开,会有什么问题?

(2)三态门全都关闭时,总线上的状态应该是什么?实际显示又是什么?如何理解这个现象?

实验任务1:二选一多路器

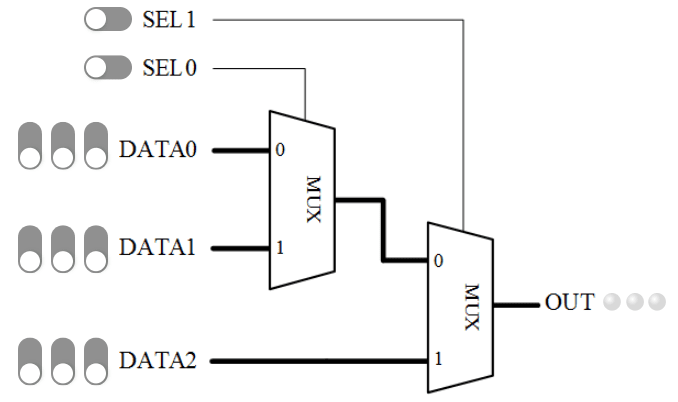

用两个二选一多路器代替三态门实现类似的功能,如图 2。 具体要求如下。

(1)用持续赋值语句和条件表达式描述二选一多路器,按照图 2连接两个二选一多路器。

(2)为便于机器考核,要求DATA0、DATA1、DATA2和OUT所用的虚拟元件序号与例 1相同,SEL0用OE0的开关,SEL1用OE1的开关。

(3)在实验系统验证设计的正确性;并分析与三态门的结果有什么异同。思考什么情况可以用多路器的方案代替三态门。

| 多级条件表达式或嵌套if-else语句描述的串行电路理论上会产生累加的电路时延,所以通常不提倡图 2所示的级联设计。三路以上的多路选择器应采用case语句描述。 |

实验任务2:与或门实现数据选择器

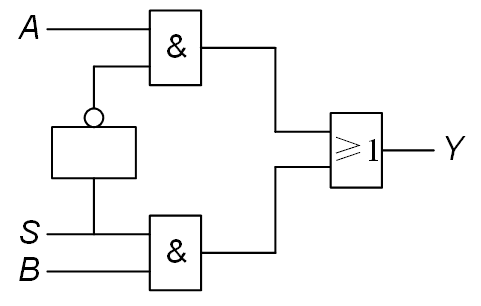

如果从电路结构的角度看,上面的二选一多路器是由与门、或门或反相器构成,如图 3所示。

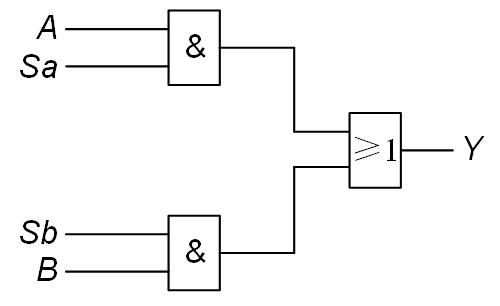

如果将反相器去掉,增加一个选择信号,也可以实现数据选择的功能,如图 4。常规的多路器总会选择某一路输出,也只能选择其中一路输出;图 4数据选择器的特殊之处在于可以任何一路都不选择,也可以多路同时影响输出。

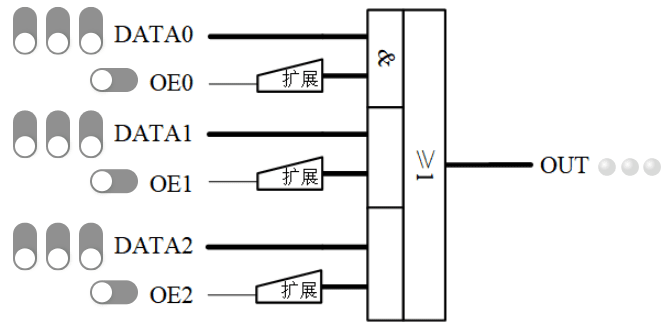

用类似的与或结构,可以增加输入通道的数量。实验任务的虚拟面板如图 5所示,具体要求如下。

(1)按照虚拟面板图中的电路结构用与或表达式描述3选1多路选择器。

图中“扩展”表示将1位的 oe 信号复制为3位,然后再和3位的 data 进行按位逻辑与运算。在Verilog中可以用并接、复制运算符描述“扩展”,如 {3{oe0}}。

| 尽管与或逻辑很简单,却有很多应用场合。在后面的实验中也会多次用到,应熟练掌握。 |

(2)为便于机器考核,输入输出所用的端口应与例 1相同。

(2)用实验系统验证。 通过验证体会电路特性与前面两种方案的不同。