流密码器实验

本实验为信息安全专业选做实验。

实验原理

流密码是将明文划分成字符(如单个字母)或其编码的基本单元(如0, 1数字),逐个与密钥流作用进行加密,接收端使用同样的密钥流解密,属于对称加密技术。流密码强度完全依赖于密钥序列的随机性和不可预测性,其核心问题是密钥流生成器的设计。线性反馈移位寄存器(LFSR,Linear Feedback Shift Register)因其实现简单、速度快、有较为成熟的理论等优点而成为构造密钥流生成器的最重要的部件之一。LFSR可以生成伪随机序列,n级LFSR其输出伪随机序列的周期小于等于2n-1,通过选择合适的反馈函数可使序列的周期达到最大值2n-1,该序列称为m序列。反馈函数可用一个一元高次多项式表示,称这个多项式为LFSR的特征多项式,其中本原多项式产生的非零序列均是m序列。一般可通过查表的方式得到常用的本原多项式的反馈系数。

参考设计

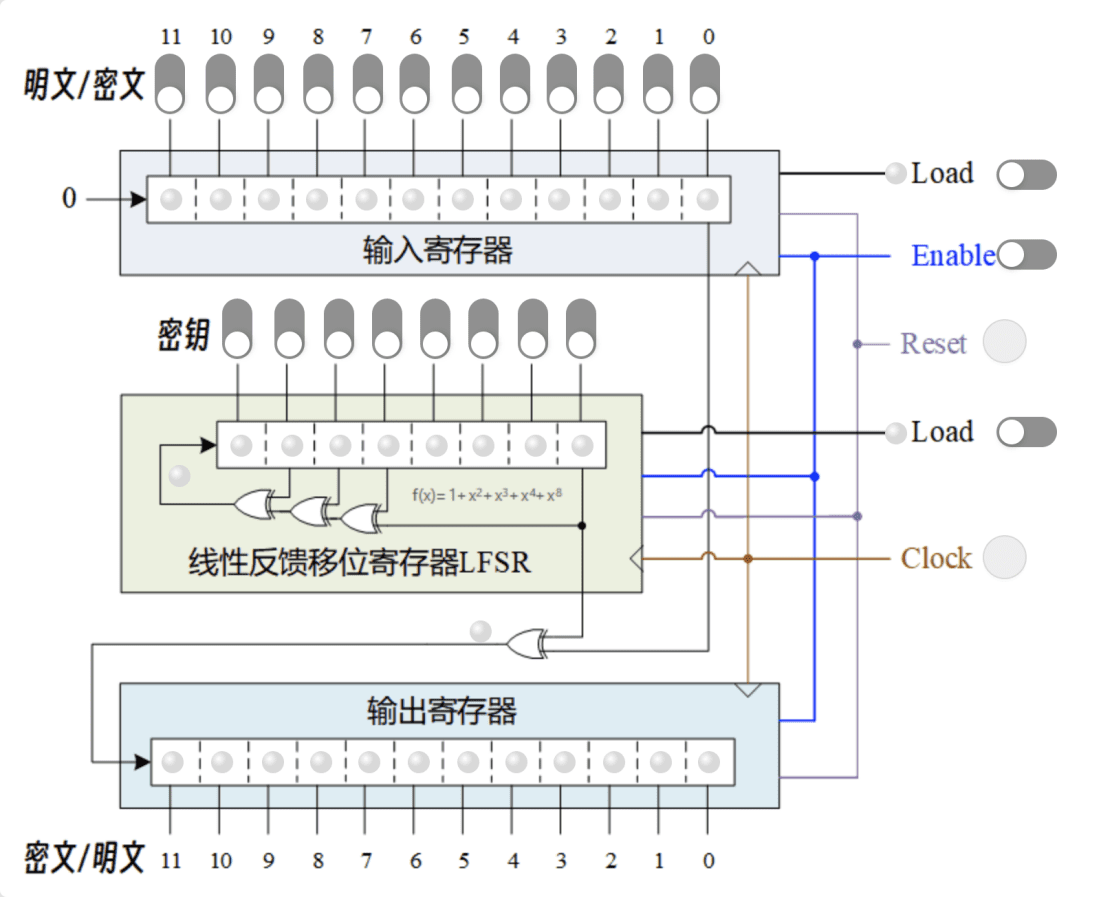

虚拟面板如图 1。

/****** Replace input ports with internal signals *******/

wire reset = PB[0];

wire clk = PB[1];

wire [11:0] in_reg_d= S[11:0];

wire [7:0] lfsr_d = S[26:19];

wire in_reg_load = S[16];

wire lfsr_load = S[17];

wire shift_enable = S[18];

/************* The logic of this experiment *************/

wire [11:0] in_reg_q, out_reg_q;

wire [7:0] lfsr_q;

wire lfsr_left_in, cipher_stream;

RightShifter #(12) IR (.iClk(clk), .iReset(reset),

.iLoad(in_reg_load), .iEnable(shift_enable),

.iShiftIn(1'b0), .iD(in_reg_d), .oQ(in_reg_q));

RightShifter #(8) LFSR (.iClk(clk), .iReset(reset),

.iLoad(lfsr_load), .iEnable(shift_enable),

.iShiftIn(lfsr_left_in), .iD(lfsr_d), .oQ(lfsr_q));

assign lfsr_left_in = lfsr_q[0]/*- TODO:根据反馈系数设计线性反馈移位寄存器 -*/;

assign cipher_stream = in_reg_q[0] ^ lfsr_q[0];

RightShifter #(12) OR (.iClk(clk), .iReset(reset),

.iLoad(in_reg_load), .iEnable(shift_enable),

.iShiftIn(cipher_stream), .iD(12'h0), .oQ(out_reg_q));

/***** Internal signals assignment to output ports ******/

assign L[11:0] = in_reg_q;

assign L[19:12] = lfsr_q;

assign L[31:20] = out_reg_q;

assign L[32] = in_reg_load;

assign L[33] = lfsr_load;

assign L[34] = lfsr_left_in;

assign L[35] = cipher_stream;

|

任务2:流密码器的控制

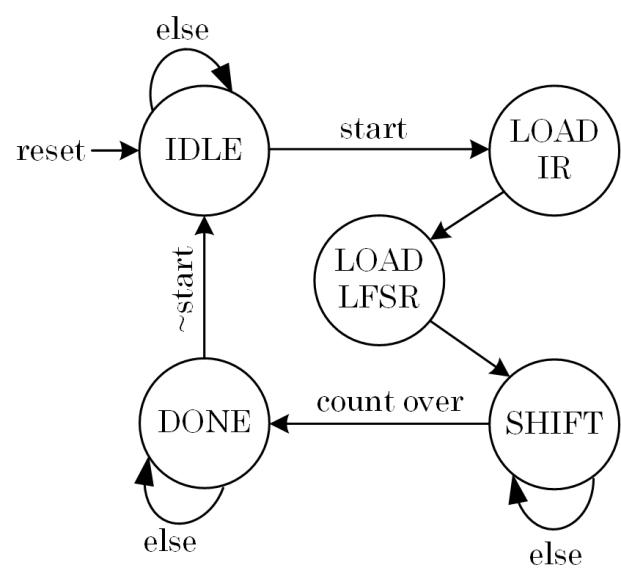

在任务1中,用按键产生时钟信号,人工计数12次移位。这个任务用连续的时钟作为移位寄存器的时钟信号,并且用一个计数器控制移位的次数,当移位12次后自动停止移位,用有限状态机设计一个控制逻辑来实现这个过程,其状态图如图 2。

图中start是启动信号,用开关产生。“LOAD IR”状态将开关数据装入输入寄存器;“LOAD LFSR”状态将开关数据装入线性反馈移位寄存器;“SHIFT”状态移位所有的寄存器,移位次数由一个减法计数器控制,当移位12次后进入“DONE”状态;在“DONE”状态,如果start信号尚未撤销,则停留在这个状态,直到start信号撤销再回到空闲状态。

将状态机输出填入下表,并用HDL设计实现该状态机。

| IDLE | LOAD IR | LOAD LFSR | SHIFT | DONE | |

|---|---|---|---|---|---|

| 前面计数器实验中已经完成将10MHz的时钟分频为1Hz时钟的分频器。 |