硬布线控制实验

本实验为软件工程专业选做实验。

单周期数据通路

“周期”是指时钟周期,如果完成一次运算只需要一个时钟周期,就称为单周期数据通路;需要几个时钟周期才能完成一次运算则称为多周期数据通路。单周期数据通路很容易演变为流水线数据通路,多为RISC处理器采用。

本实验分为单周期数据通路和硬布线控制两部分。在数据通路部分,通过开关手动输入控制信号完成运算过程是;然后在硬布线控制部分,通过指令指挥控制器产生控制信号完成运算过程。

原理

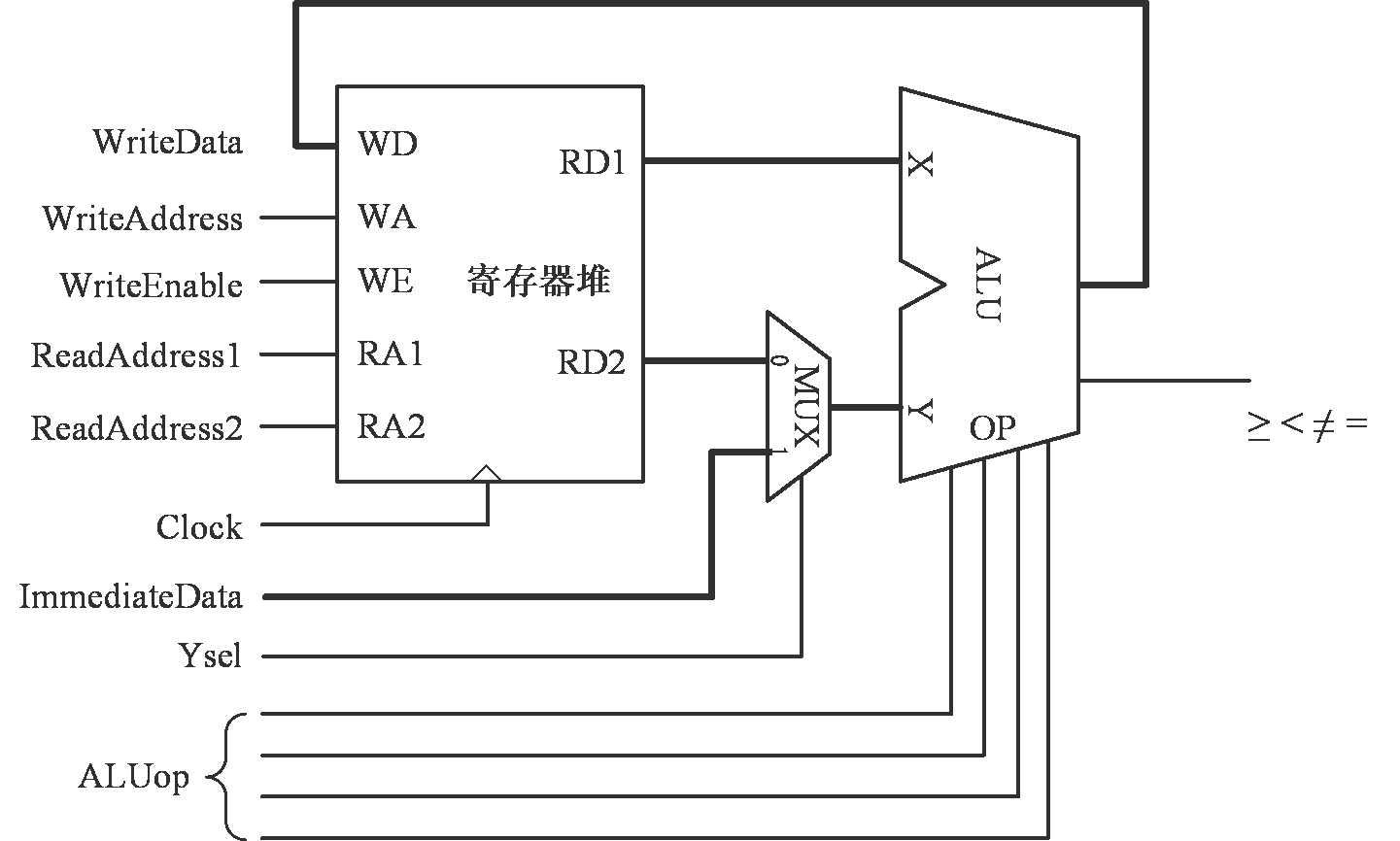

图 1是本实验的单周期数据通路,该数据通路使用了前面实验中的ALU和三端口寄存器堆,2个读端口向ALU的两个输入端提供运算数据,1个写端口接收ALU的运算结果,可以一个周期完成读数据、运算、存结果。ALU模块使用前面算术逻辑单元实验中自己设计的ALU,ALUop的编码和比较运算均按照前面实验的要求;三端口寄存器堆使用存储器实验中完成的。实验材料给出了VirtualBoard模块的代码,包含了对ALU和寄存器堆的实例化。

硬布线控制

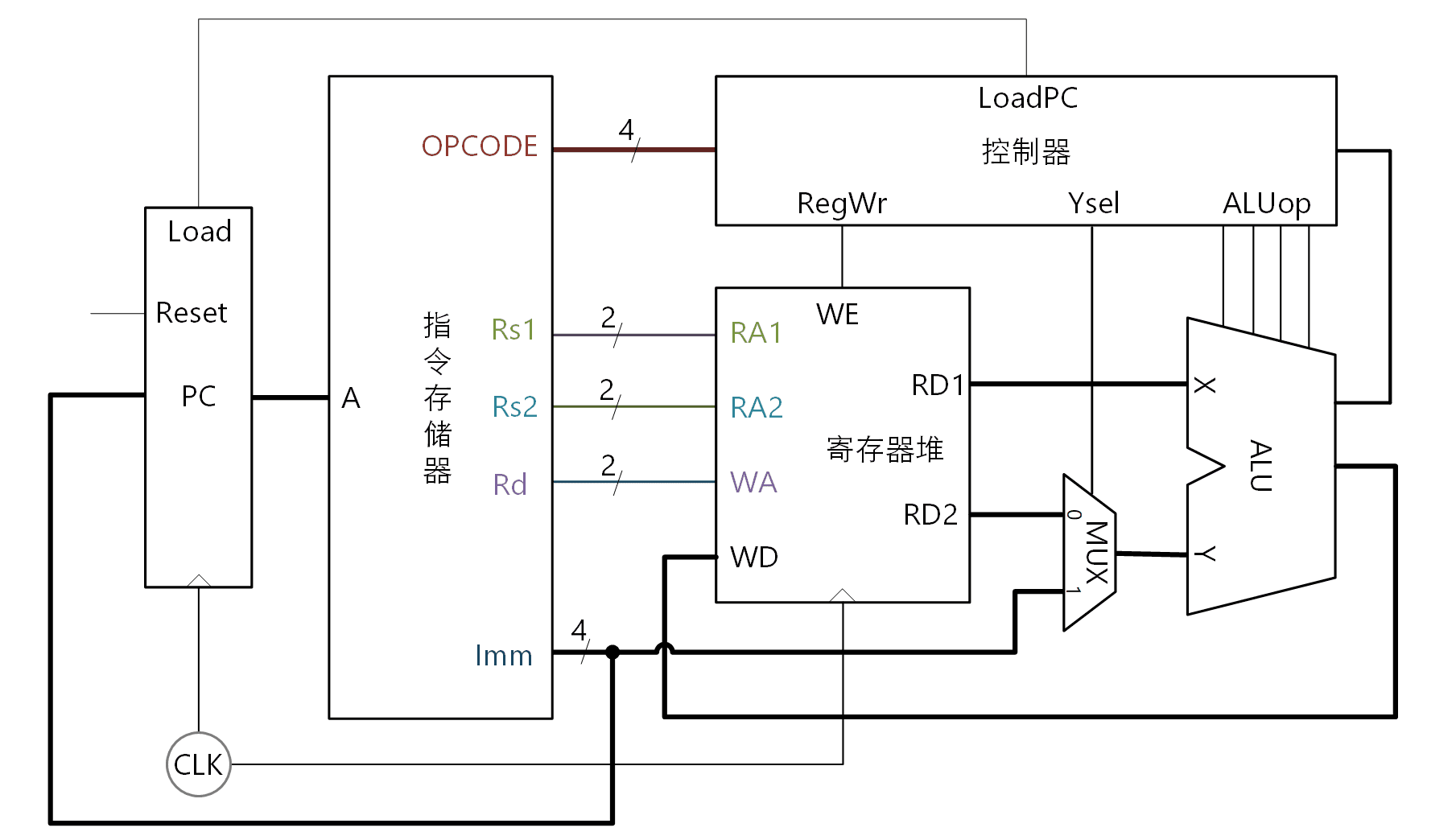

在上面数据通路的基础上,增加指令存储器、控制器等部件,可以看成是一个简单的CPU。原理框图如图 2。

指令系统

包含运算器和控制器的实验电路看成是一个简单的CPU,根据ALU所能够实现算术及逻辑运算功能,以及运算器数据通路的结构,设计了R型和I型运算指令以及B型分支指令,指令格式如下。

13 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

0 |

|

OPCODE |

Rs1 |

Rs2 |

Rd |

Imm |

||||||

指令功能及操作码编码见表 1。R型指令的两个源操作数均来自寄存器,分别由Rs1和Rs2给出寄存器号。I型指令的一个源操作数来自寄存器,由Rs1给出寄存器号;另一个源操作数是立即数,由指令的Imm字段提供。运算结果存入由Rd指定的寄存器中。B型指令根据rs1和rs2的大小关系决定是顺序执行下一条指令,还是跳转去执行地址为Imm的指令。

| 指令类型 | 指令助记符 | OPCODE | 功能 |

|---|---|---|---|

R型 |

add rd, rs1, rs2 |

0001 |

rd←(rs1)+(rs2) |

sub rd, rs1, rs2 |

0010 |

rd←(rs1)-(rs2) |

|

and rd, rs1, rs2 |

0011 |

rd←(rs1)∧(rs2) |

|

or rd, rs1, rs2 |

0100 |

rd←(rs1)∨(rs2) |

|

xor rd, rs1, rs2 |

0101 |

rd←(rs1)⊕(rs2) |

|

I型 |

addi rd, rs1, #imm |

0110 |

rd←(rs1)+imm |

andi rd, rs1, #imm |

0111 |

rd←(rs1)∧imm |

|

ori rd, rs1, #imm |

1000 |

rd←(rs1)∨imm |

|

xori rd, rs1, #imm |

1001 |

rd←(rs1)⊕imm |

|

B型 |

beq rs1, rs2, #imm |

1010 |

if (rs1=rs2) goto imm |

bne rs1, rs2, #imm |

1011 |

if (rs1≠rs2) goto imm |

|

blt rs1, rs2, #imm |

1100 |

if (rs1<rs2) goto imm |

|

bge rs1, rs2, #imm |

1101 |

if (rs1≥rs2) goto imm |

指令部件

指令存储器的字长是14位,有16个存储单元,可以存放16条指令。因此指令存储器的地址需4位,由程序计数器PC提供。复位时PC值为0,即第一条指令的地址。在Clk上升沿到来时,如果Load为1,则将Imm装入PC,实现程序转移;否则PC值加1,即顺序执行。

指令存储器是只读存储器,可以使用存储器实验中的ROM模块,在初始化部分写入要执行的指令编码。下面的例子给出了4条指令的编码。

logic [13:0] mem[0:15]; initial begin // 13__10 9_8 7_6 54 3_0 // OPCODE Rs1 Rs2 Rd Imm mem[0] = 14'b0110_00_00_01_0101; // addi r1, r0, #5 mem[1] = 14'b1000_00_00_10_1010; // ori r2, r0, #10 mem[2] = 14'b0010_01_10_11_0000; // sub r3, r1, r2 mem[3] = 14'b1011_10_11_00_0000; // bne r2, r3, #0 end

控制器

控制器以指令opcode作为输入,为数据通路中所有单元产生控制信号。

图 2单周期数据通路中,需要如下控制信号:

(1)PC的load信号:为0时,PC加1;为1时,PC装载来自imm的立即数。

(2)寄存器堆的写入信号:为1时,寄存器堆执行写入操作。

(3)多路器的选择信号:为0时,ALU的Y操作数,来自寄存器堆的RD2输出;为1时,ALU的Y操作数,来自立即数imm。

(4)ALU的运算控制信号ALUop:根据之前ALU实验的设计要求,操作对应的编码为:

| ALUop(4位) | 功能 |

|---|---|

0001 |

ADD |

0010 |

SUB |

0011 |

AND |

0100 |

OR |

0101 |

XOR |

数据通路中的指令存储器,内容在设计时预先写入,只提供读访问,根据输入地址,输出该地址单元存储的内容,不需要控制器产生控制信号。

因为指令系统的简单和规整,对控制器的设计,就是设计译码过程来确定控制信号。对于指令系统中的R型和I型指令,控制器根据opcode的值,译码产生数据通路上的各个控制信号,实现指令功能。对于指令系统中的B型指令,控制器还需要来自ALU产生的标志位或者比较结果,与Opcode的值一起,译码产生控制信号。

实验任务

用HDL设计图 2电路。控制器根据opcode产生相应的控制信号。在实验平台验证设计。