ModelSim仿真入门

有两种方式启动ModelSim:从Quartus启动,或者独立使用。从Quartus启动ModelSim仿真的方法事先需要在Quartus中做一些设置,但是启动ModelSim之后需要做的操作比较少,有利于反复进行仿真,这里以这种方式为主进行介绍,最后再补充说明脱离Quartus独立使用ModelSim的方法。

这里举例使用的设计环境为:Quartus Prime 20.1 和ModelSim - Intel FPGA Starter Edition 2020.1。

准备工作

创建或打开Quartus II工程

这里以计数器实验的参考设计为例。

编译设计工程

如果是功能仿真,只需要逻辑综合;点击Processing ➤ Start ➤ Start Analysis & Synthesis菜单项或工具栏相应按钮,对设计进行综合。

如果要做时序仿真,因为时间参数是Quartus布局布线后的产生的,所以必须进行全编译,点击Processing ➤ Start Compilation菜单项或工具栏相应按钮全编译工程。

编写Testbench

如果是功能仿真,可以只对工程中某个模块进行仿真,而时序仿真则必须仿真整个工程。在编写Testbench时需注意这一点。

计数器实验的实验材料中提供了功能仿真的testbench,将文件拷贝到工程文件夹内。

仿真环境设置

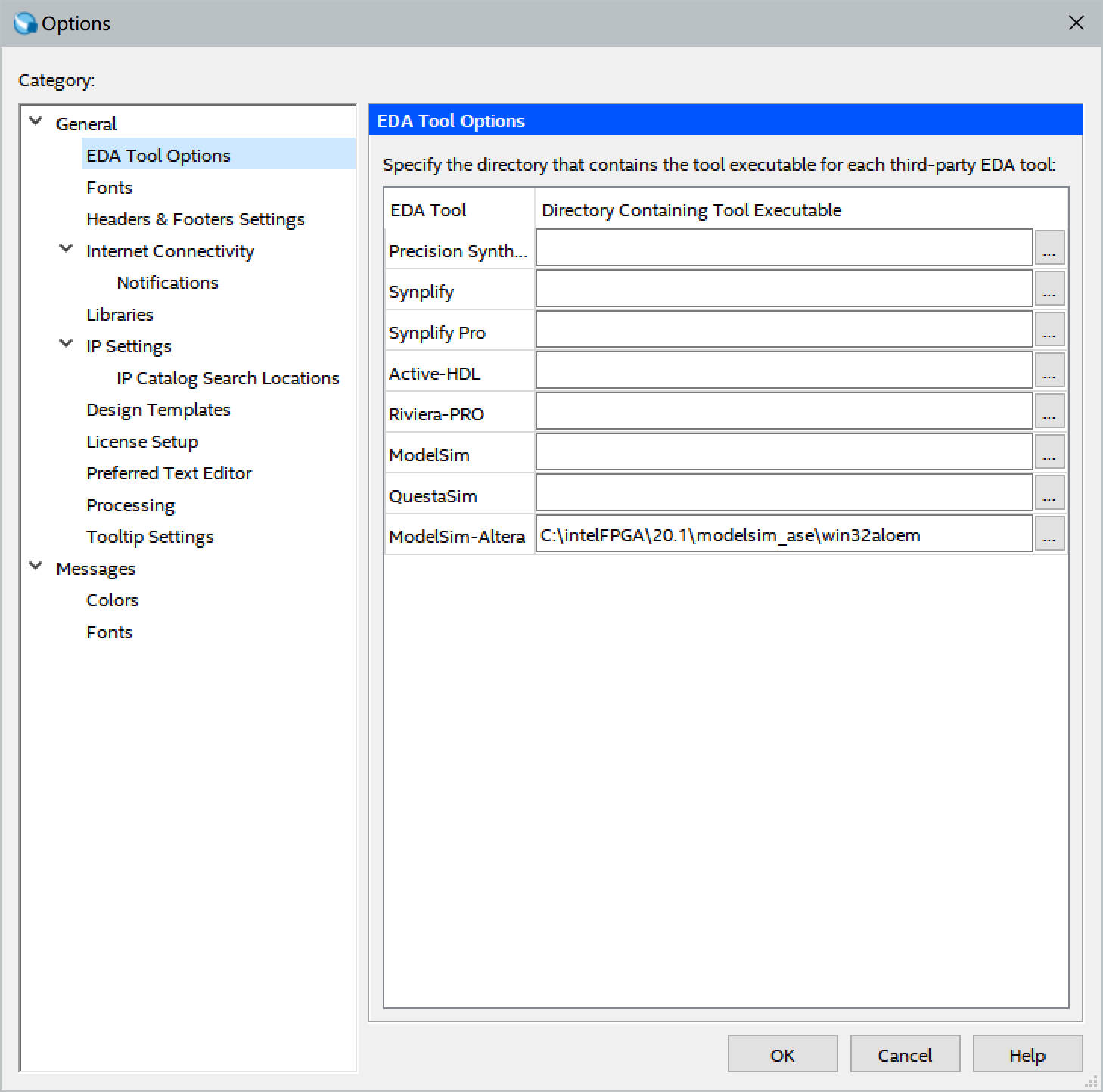

设置ModelSim的路径

通过菜单Tools ➤ Options… 在EDA Tool Options中设置modelsim.exe可执行文件的路径,点击ModelSim-Altera编辑框右端的 … 按钮,在文件资源管理器中找到modelsim.exe,一般是在Quartus安装目录下的modelsim_ase\win32aloem文件夹。图 1仅为示例,应根据自己电脑中安装路径进行设置。

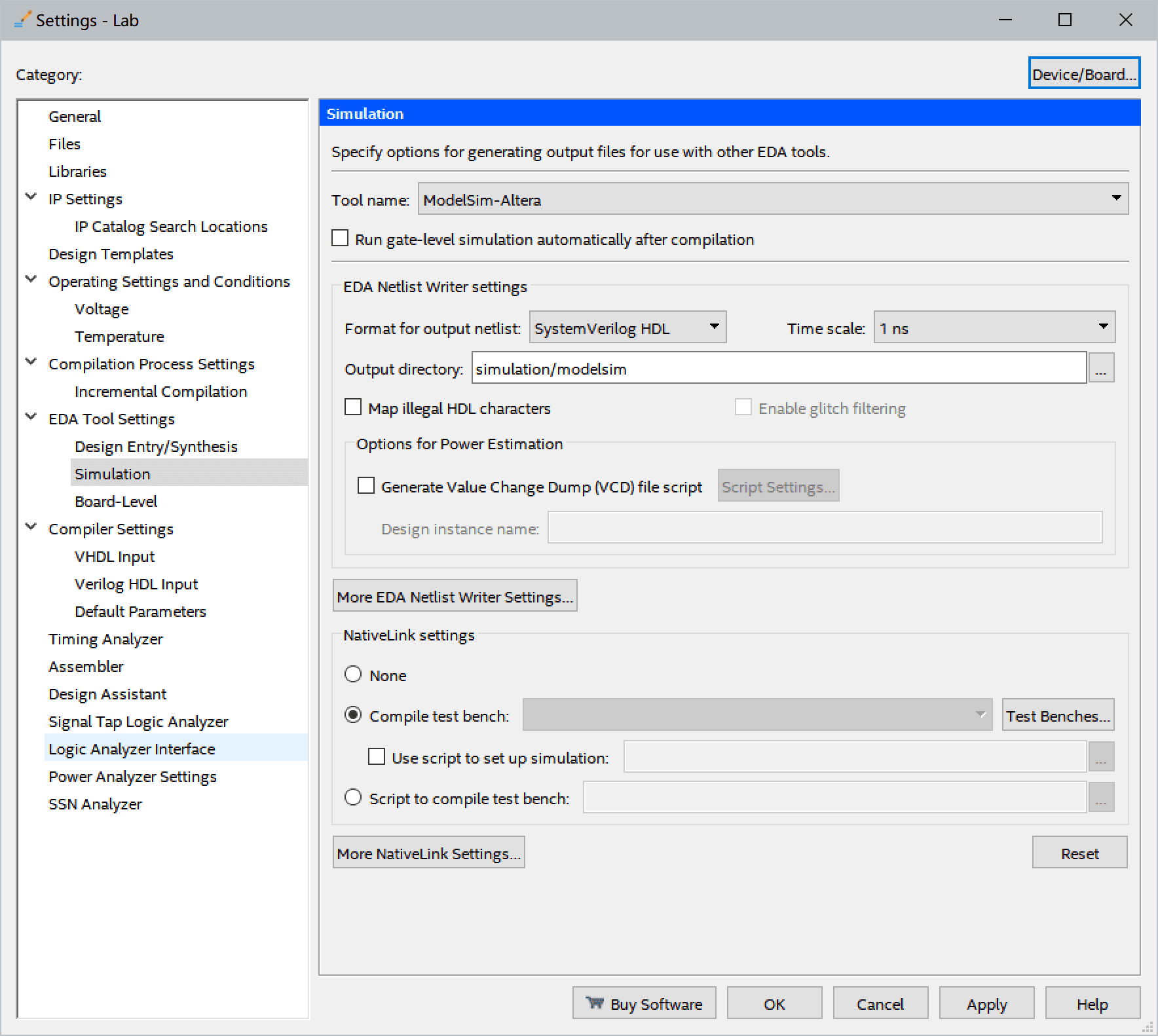

设置ModelSim 仿真属性

通过菜单Assignmenets ➤ Settings… 打开设置对话框,如图 2。在EDA Tool Settings的Simulation选项中进行如下设置。Tool name选择ModelSim-Altera;Format for output netlist选择SystemVerilog HDL;Time scale是仿真的时间单位,如果在Testbench里没有写`timescale语句来定义时间单位,那么仿真器会按照这里设置的时间单位进行仿真。推荐在testbench中写`timescale语句。

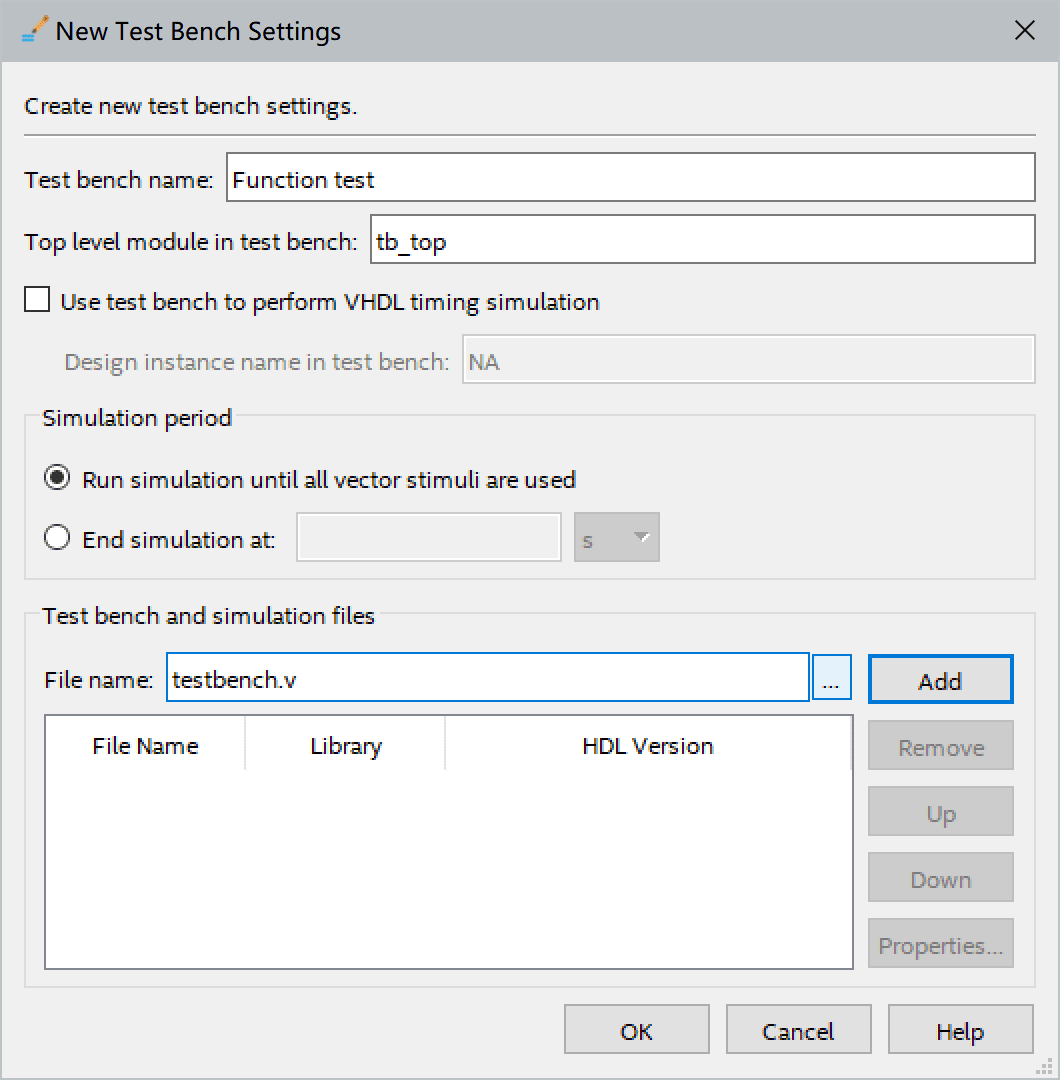

在NativeLink settings中,选择Compile test bench,点击Test Benches… 按钮,新建一个Test Bench设置,对Test Bench Settings对话框中的设置选项进行手工填写,如图 3。包括:

Top level module in test bench —— 在这里指明Testbench的模块名。注意这个名称不是指设计模块的顶层,而是Testbench的顶层模块名。之所以称作“Top level module”,是因为Testbench可能包含多个模块;本实验Testbench只有一个模块。

Simulation period ——设定仿真时间。可以选择运行完所有的激励向量或者设定仿真结束时间。

点击Test bench and simulation files中的文件浏览按钮 …,找到事先写好的Test bench文件,点击Add按钮,将其加入文件列表。如果Test bench有多个文件,须全部加入。本实验只有一个Test bench文件,在前面准备工作中已经放入工程文件夹内。

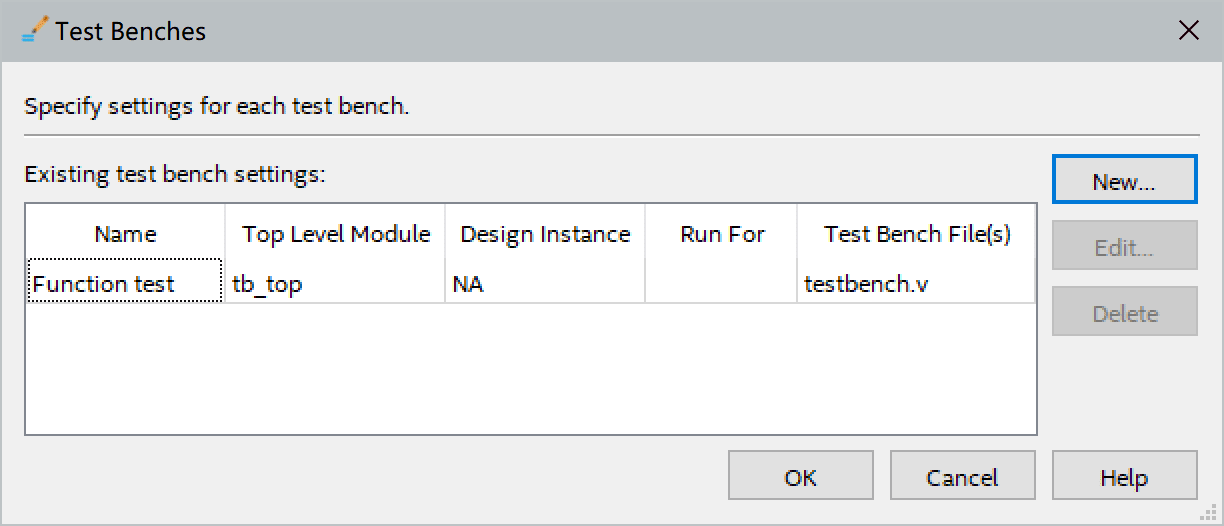

点击OK按钮完成Test Bench Settings填写后,刚才完成的设置出现在Existing test bench settings列表中,如图 4,以后还可以通过Edit和Delete按钮对设置进行编辑修改或删除。

运行仿真

启动ModelSim仿真工具

在Quartus中,功能仿真对应菜单项Tools ➤Run Simulation Tool ➤ RTL Simulation,时序仿真对应菜单项Gate Level Simulation。一般应先进行功能仿真,点击相应菜单项,Quartus 根据之前对仿真器和Testbench的设置,自动调用ModelSim进行功能仿真。

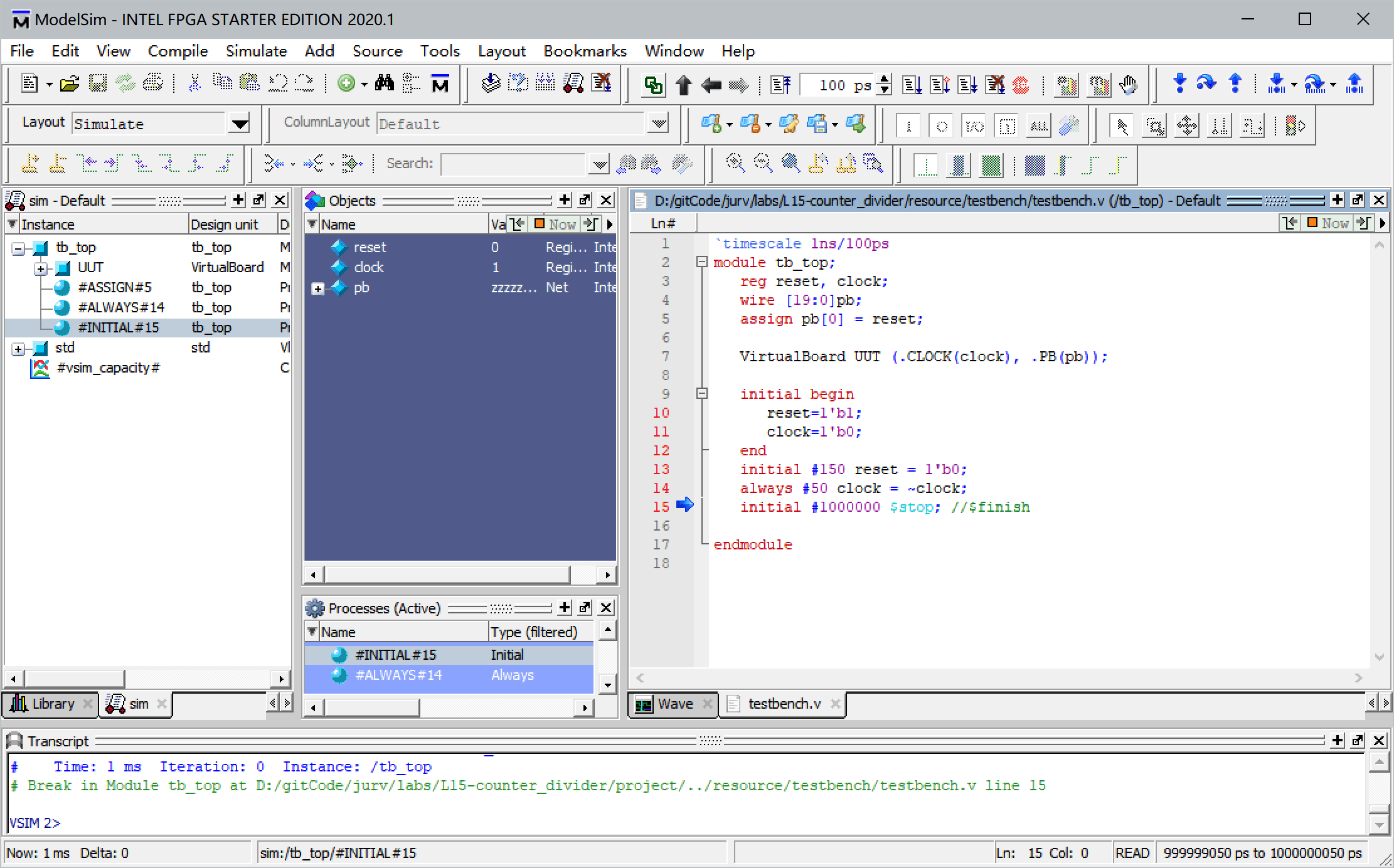

ModelSim启动后,默认条件下,界面如图 5,可以看到sim窗口(Structure)、对象窗口(Objects)、波形窗口(Wave)、代码窗口(Files)和脚本窗口(Transcript)。如果某个窗口被关闭,可以通过View菜单项打开,括号中的英文是View菜单的子项名称。

sim窗口可以显示仿真模块的层次并选择某个模块观察,对象窗口用来显示当前模块中包含的各个信号,信号的显示会随着主窗口工作区中选中的不同层次的不同模块而自动发生变化。

下方Transcript窗口中记录了ModelSim命令的执行结果。如果启动后界面和预期不同,可检查Transcript窗口中是否有错误信息。此外,Transcript窗口中也可以在提示符下输入ModelSim命令,为有经验的用户提供了另一种操作方式。

波形窗口

波形窗口用来直观的显示仿真波形,是最常用的仿真窗口之一。点击“Wave”选项卡使波形窗口成为活动窗口。波形窗口分为三个区域,分别用来显示信号名称以及路径,显示光标所在位置信号的当前值,以及显示波形。

点击Wave窗口右上角的![]()

![]() 按钮,可以扩展、还原Wave窗口,点击

按钮,可以扩展、还原Wave窗口,点击![]() 按钮,可将Wave窗口变为浮动窗口。工具栏中的

按钮,可将Wave窗口变为浮动窗口。工具栏中的 ![]() 用来放大、缩小波形、显示全部波形以及光标为中心放大波形。通过缩小波形可以观察到仿真波形如图 6,窗口自动包含了Testbench里定义的信号。

用来放大、缩小波形、显示全部波形以及光标为中心放大波形。通过缩小波形可以观察到仿真波形如图 6,窗口自动包含了Testbench里定义的信号。

Wave窗口左下方区域有三个小按钮![]() ,第一个按钮用来选择是否显示信号的路径;第二个按钮用来设置Wave窗口的属性,例如更改显示时间单位;第三个按钮用来添加时间光标。

,第一个按钮用来选择是否显示信号的路径;第二个按钮用来设置Wave窗口的属性,例如更改显示时间单位;第三个按钮用来添加时间光标。

在Wave窗口信号名称区域中选中某些观察信号后,可以使用右键菜单Radix改变所观察信号的基数(radix)。

添加观察信号

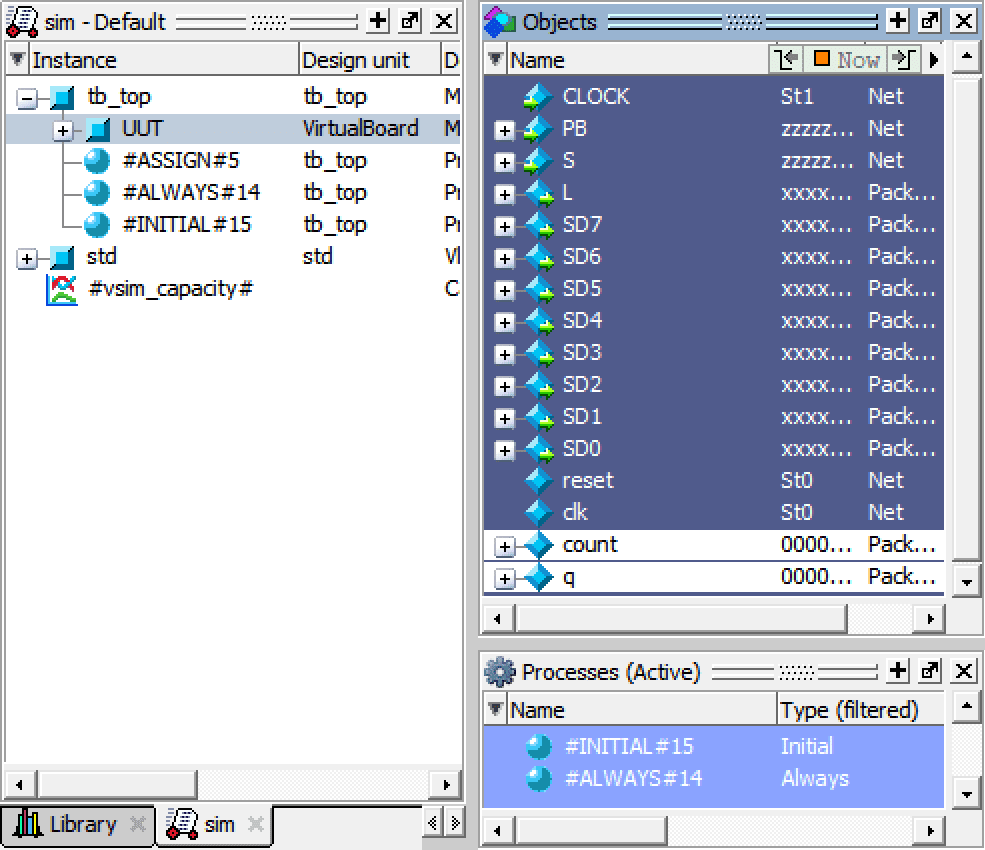

可以添加更多的内部信号来观察,如计数值等。在sim窗口依次展开设计层次树形结构:testbench - UUT,单击选中UUT模块后,该模块内部的信号就会出现在Objects 窗口,如图 7。在Objects窗口中选择想要观察的信号,如count和q信号,右击鼠标,右键菜单项Add Wave将所选信号加入Wave窗口。

也可以将Objects窗口的信号直接拖到到Wave窗口中去。ModelSim除主窗口之外的各个窗口内的对象都可以从一个窗口直接拖动到另外的窗口,使用起来和Windows资源管理器类似。

仿真结果分析

观察分析仿真结果

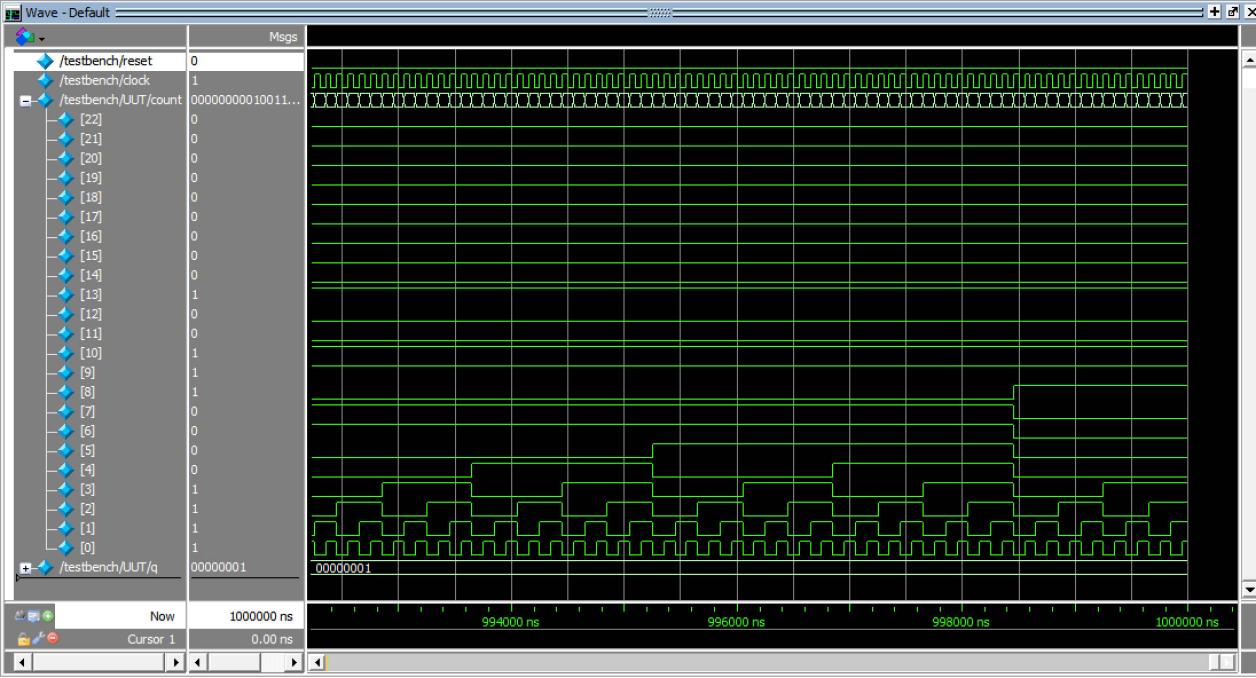

重新启动仿真后的波形如图 8。

从波形上看移位寄存器的输出q(图中最后一行)一直是00000001没有变化,也就是复位的初值。这是因为仿真的时间不够长,计数器count还没有溢出。可以继续运行仿真,也可修改testbench,延长停止仿真前的时长。

仿真调试工具

如果仿真结果和预期不同,如何查找问题的原因呢?通过阅读代码和分析波形虽然也可以找到设计中存在的简单问题,但是充分利用工具,可以达到事半功倍的效果。

使用ModelSim设置断点与源代码单步执行进行调试

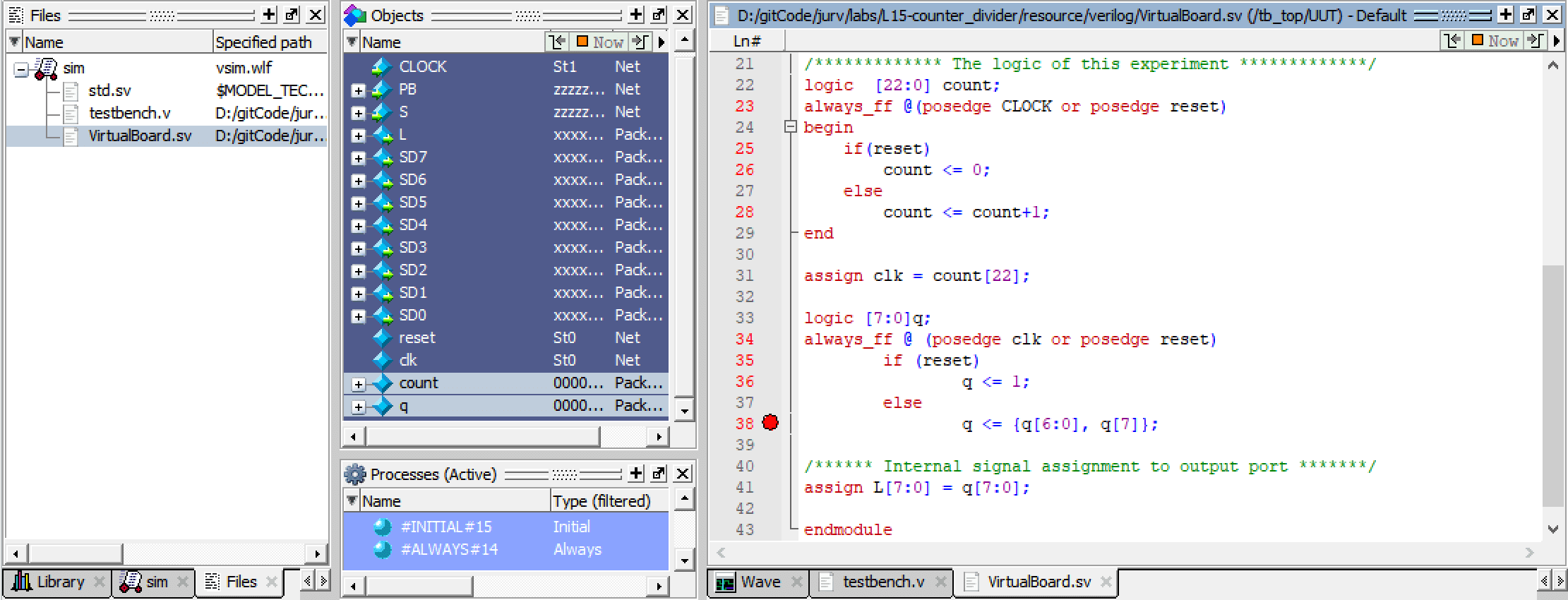

ModelSim环境提供交互式的调试功能,用户可以在源代码窗口设置断点,运行仿真并调试。点击View ➤ Files菜单项,出现Files文件窗口,展开树形结构,可以看到工程中的设计文件,如图 9,双击verilog设计文件在源代码窗口打开文件。

在源代码窗口中,单击某条语句所在的行号,会出现红色圆点,即在该语句处设置断点。单击红色圆点可以使断点在“禁止/使能”两状态间切换,右击红色圆点并选择“Remove Breakpoint”可以删除断点。

断点设置完成后,点击Restart 按钮![]() 重新启动仿真,点击Run或者Run -All按钮,仿真将运行直到遇到断点停止,同时在源代码窗口中用箭头指向断点语句。

重新启动仿真,点击Run或者Run -All按钮,仿真将运行直到遇到断点停止,同时在源代码窗口中用箭头指向断点语句。

在源代码窗口选中某个信号,如count,右击鼠标,在弹出的菜单中选择“Examine”命令,系统弹出Source Examine窗口,通过该窗口可以查看信号的当前的值。点击工具栏上![]() 按钮可以单步执行仿真。

按钮可以单步执行仿真。

脱离Quartus独立使用ModelSim仿真的步骤

这里举例的仿真环境使用ModelSim - Intel FPGA Starter Edition 2020.1,该版本与Quartus Prime 20.1 配套。

创建ModelSim工程并为工程添加文件

从Windows开始菜单启动ModelSim - Intel FPGA Starter Edition,在Welcome窗口点击Jumpstart按钮。通过菜单项File ➤ New ➤ Project… 打开创建工程对话框。在Project Name编辑框中填入工程名,Project Location框中设置工程路径,点击“OK”完成工程创建。

在弹出的“Add items to the Project”对话框中,点击“Add Exiting File”,打开添加文件对话框,将设计文件和TestBench文件加入工程。添加时可选择“Reference from current location”或者“Copy to project directory”,建议选择后者。

编译

文件添加完成后,在Project窗口可以看到加入的文件。通过菜单项Compile ➤ Compile All对工程中所有文件进行编译,或者右键点击Project窗口弹出右键菜单,点击Compile All完成对文件的编译。

启动仿真

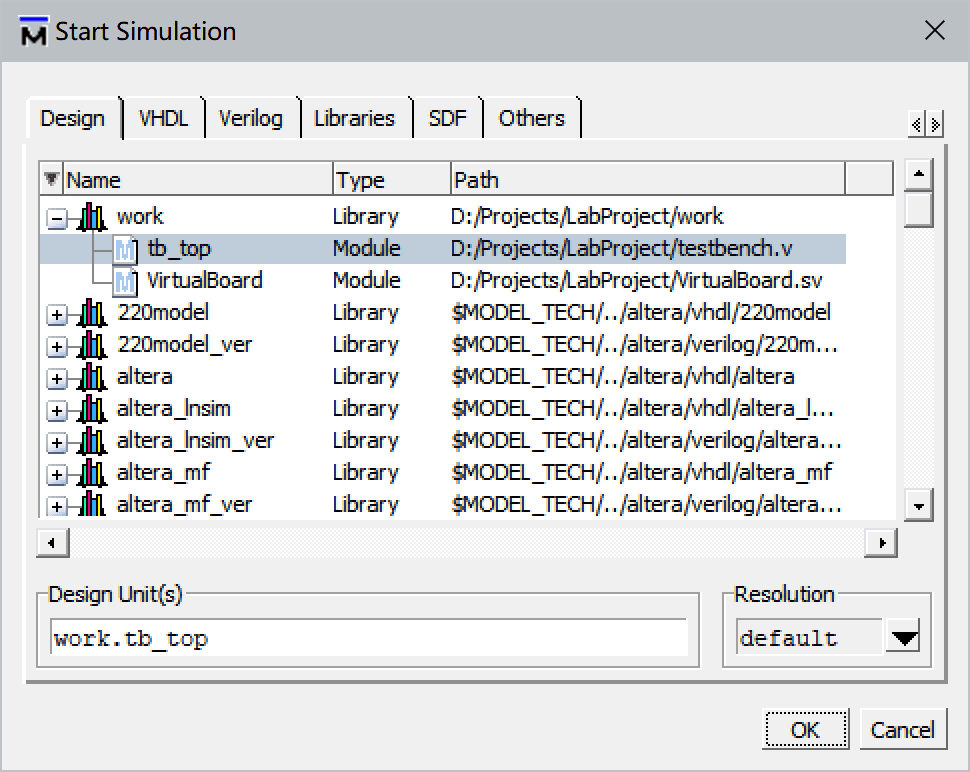

通过菜单项Simulate ➤ Start Simulation…打开启动仿真对话框,在work中选择Testbench模块,如图 10,点击“OK”,启动仿真。

通过菜单项View ➤ Wave打开波形窗口,ModelSim不会自动地添加观察信号,用前面介绍的方法添加观察信号。如果以前保存过波形窗口格式,可通过菜单项File ➤ Load ➤ Macro File(或者Tools ➤ TCL ➤ Execute Macro…)导入.do宏文件。

独立使用ModelSim也不会自动运行仿真,需要在工具栏中点击运行按钮。之后的操作就与从Quartus启动ModelSim仿真一样啦,不再重复说明。