三态门和多路器实验

实验内容和要求

三态门

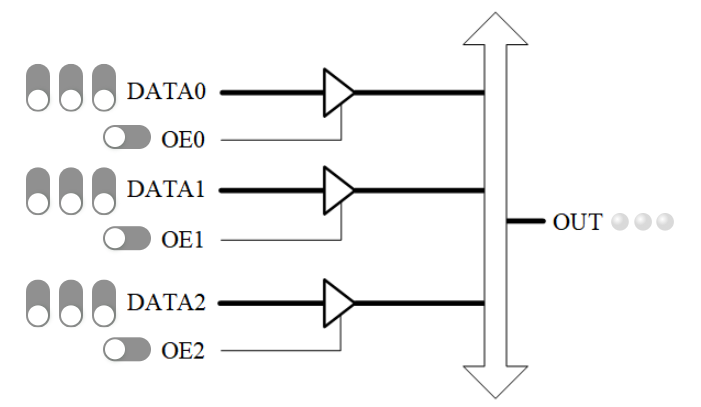

实验原理图如图 1。

图 1. 三态门的虚拟面板

实验材料中给出了图 1的HDL代码。读懂代码后用实验系统验证,通过验证理解三态门的特性和正确用法。特别地,考虑以下问题,并通过实验找出答案。

(1)如果有2个或2个以上的三态门同时打开,会有什么问题?

(2)三态门全都关闭时,总线上的状态应该是什么?实际显示又是什么?如何理解这个现象?

二选一多路器

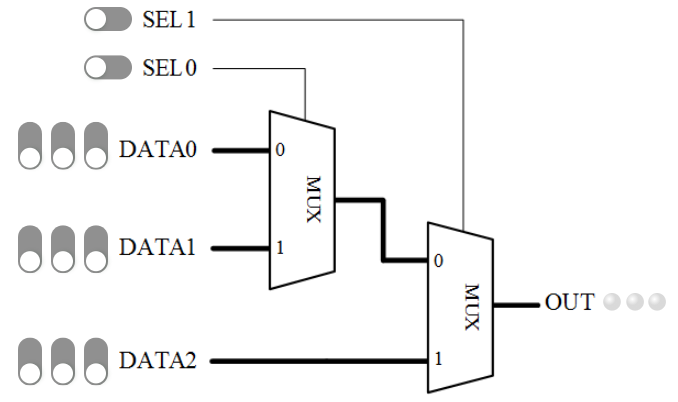

用两个二选一多路器代替三态门实现类似的功能,如图 2。

图 2. 二选一多路器的虚拟面板

用持续赋值语句和条件表达式描述二选一多路器,按照图 2连接两个二选一多路器。为便于考核,要求DATA0、DATA1、DATA2和OUT所用的虚拟元件序号与图 1三态门虚拟面板的相同,SEL0用OE0的开关,SEL1用OE1的开关。

打开实验材料中提供的虚拟面板“二选一多路器.jvp”,验证设计的正确性;并分析与三态门的结果有什么异同。思考什么情况可以用多路器的方案代替三态门。

与或门实现数据选择器

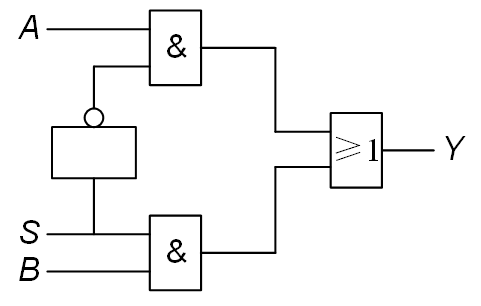

如果从电路结构的角度看,上面的二选一多路器是由与门、或门或反相器构成,如图 3所示。

图 3. 二选一多路器的电路结构

如果将反相器去掉,增加选择信号,也可以实现数据选择的功能,如图 4。

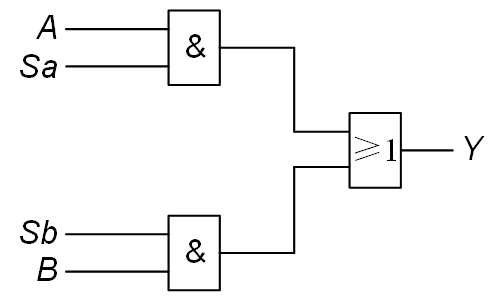

图 4. 与或门实现的二选一数据选择器

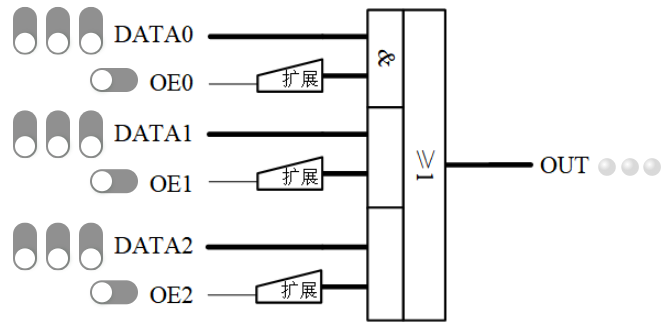

常规的多路器总会选择某一路输出,也只能选择其中一路输出;图 4数据选择器的特殊之处在于可以任何一路都不选择,也可以多路同时影响输出。这种方法在后面的实验中会反复用到,应熟练掌握。根据这种方法设计3选1多路选择器,编译后用实验系统验证,虚拟面板如图 5所示。图中“扩展”表示将1位的信号复制为3位,在Verilog中可以用并接、复制运算符描述,如 {3{oe0}}。

图 5. 与或门数据选择器的虚拟面板