Quartus FPGA设计流程

准备工作

安装FPGA设计软件

Quartus Prime的下载和安装见安装软件。

下载实验材料、创建工程文件夹

实验材料的下载方法见下载实验材料。

后文提到的实验材料名称均为适用于远程实验板或口袋实验板的实验材料,DE2-115开发板对应的实验材料名称如表 1,在后面也会以提示的形式给出。

| 实验板 | 远程或口袋实验板 | DE2-115开发板 |

|---|---|---|

文件夹 |

LabProject |

LabPrj_DE2-115 |

顶层模块 |

LabBoard_TOP.v |

DE2_115_TOP.v |

时序约束 |

RemotePocket.sdc |

DE2-115.sdc |

工程配置脚本 |

RemotePocket.tcl |

DE2-115.tcl |

创建工程脚本 |

create_project_pocket.tcl |

create_project_de2-115.tcl |

新建一个文件夹作为工程文件夹,并将实验材料中的LabProject文件夹的内容复制到工程文件夹。同样要注意,工程文件夹的名称和路径均不能包含空格和汉字;也不建议把工程文件夹建在桌面上。学校实验室计算机通常安装硬盘保护系统,不要在被保护的硬盘分区创建工程文件夹,一般盘符靠后的如E盘是开放的。

|

Quartus软件安装路径不要有汉字和空格。 工程文件夹的名称和路径均不能包含汉字和空格。 |

实验步骤

新建工程

运行Quartus软件。点击菜单项File ➤ New Project Wizard…,出现introduction对话框。单击Next,进入Directory,name,Top-Level Entity设置对话框,选择前面创建的工程文件存放路径,输入工程名称和顶层模块名称。点击Next,进入Project Type对话框,选择Empty project。

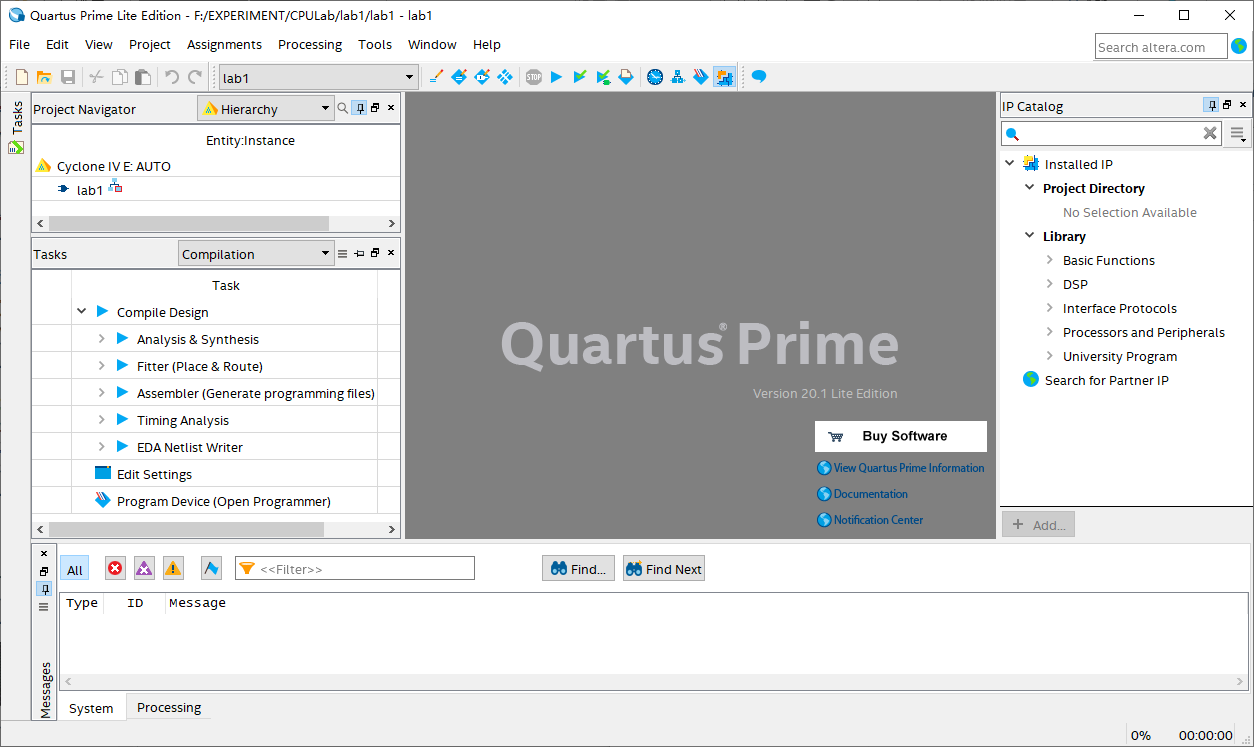

点击Finish,完成工程创建。完成后,Quartus界面如图 1所示。

配置工程

导入设计文件

点击菜单项Project ➤ ADD/Remove Files in Project…,出现category Files对话框。该对话框用来将已存在的设计文件加入到工程中。点击 … 浏览按钮,选择已经拷贝到工程文件夹内的Design Files(LabBoard_TOP.v,GlobalCLK.v,pll.v,WatchChain.sv和JutagScanChain.qxp),添加到工程中。这些文件是虚拟实验系统所需要的基础文件,用户不应该去修改它们,通常也无需理解其中的代码。

设置顶层模块

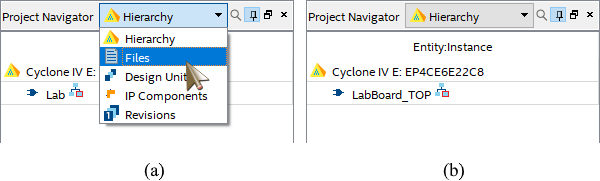

下拉Project Navigator右边的列表框,选择Files,如图 2(a),可以看到已添加到工程中的文件。右键点击LabBoard_TOP.v,在弹出菜单中选择Set as Top-Level Entity,将该文件设置为顶层模块,设置完成后的Hierarchy如图 2(b)。

| 适用于DE2-115开发板的顶层模块文件名为DE2_115_TOP.v。 |

设置输出路径

虽然设置输出路径不是必须,但可以使得工程文件夹的文件组织便于管理。点击菜单Assignments ➤ Settings或工具栏相应按钮,在打开的对话框Category栏选择Compillation Process Settings,在右边的设置项中勾选Save project output files in specified directory,在Directory name编辑框内输入“./output”。

选择硬件描述语言版本

接着在settings对话框Category栏的Compiler Settings下选择Verilog HDL Input,默认的Verilog版本是Verilog-2001,这里改为SystemVerilog。如果选择Verilog-2001,编译器将根据文件后缀名来决定使用的语言,“.v”是Verilog,“.sv”是SystemVerilog。

设置器件和引脚选项

点击菜单项Assignments ➤ Device…,出现Device对话框,根据使用的实验板在Device Family列表和Available devices列表中找到所用的FPGA器件。 远程实验板和口袋实验板的FPGA型号是Cyclone IV E系列的EP4CE6E22C8,DE2-115开发板的FPGA型号为EP4CE115F29C7。

在Device对话框中点击“Device and Pin Options …”按钮出现Device and Pin Options对话框,在对话框左侧Category列表中选择以下设置。

-

选中“Programming Files”,勾选Raw Binary File (.rbf)。远程实验板及口袋实验板需要rbf文件作为FPGA编程文件。DE2-115实验板使用JTAG方式编程,无需勾选生成rbf文件。

-

选中“Unused Pins”,设置为“As input tri-stated with weak pull-up”。

-

选中“Dual-Purpose Pins”,将“nCEO”设置为“Use as regular I/O”。

设置约束条件

约束引脚是将顶层模块(LabBoard_TOP)的输入输出端口指定到FPGA器件的实际引脚。约束引脚有手工约束和导入约束文件两种方法。

为了节省时间,本实验采用运行tcl脚本文件的方法导入约束条件,实验材料的LabProject文件夹中提供了RemotePocket.tcl文件,将该文件拷贝到工程文件夹。点击 View ➤ Tcl Console 菜单项打开 “Tcl Console” 子窗口。点击Tools ➤ Tcl Scripts菜单项,在弹出的Tcl Scripts窗口中选择RemotePocket.tcl。 点击<Run>按钮执行该脚本文件,之后会弹出一个信息框提示“Tcl Script File … executed”。 但是,这并不代表执行成功了,如果出错,会在 “Tcl Console” 子窗口显示红色的错误信息,这也是要打开“Tcl Console” 子窗口的原因。常见的错误原因是工程路径中包含了空格或汉字。也可以手工检查是否执行成功,执行菜单Assignment ➤ Assignment Editor或者Assignment ➤ Pin Planner,打开的窗口内容如果是空的,说明没有执行成功。顺便说明,Assignment Editor和Pin Planner窗口也可以用于手工约束引脚。

|

实际上RemotePocket.tcl脚本文件不仅有引脚定义信息,还包含了前面通过图形界面所做的一些设置。此外,还有一种导入引脚约束的方法是用菜单Assignments ➤ Import Assignments导入qsf或csv等文件,本实验不做练习。

需要说明的是,本书的实验采用虚拟实验方式,同学们的设计并不直接使用顶层端口,但是仍然需要进行引脚约束,否则使用虚拟实验调试系统的时候会出现问题。

保存工程

至此新的工程框架才算真正建立完成,从上面的过程可以看出,工程的配置比较繁琐,需要花费一定的时间,而且稍有差错就会导致实验失败。所以要把本实验所建的工程保存好,以便后面的实验继续使用。执行菜单File ➤ Save Project和File ➤ Close Project保存工程后关闭工程。

| 如果自己创建的工程在后面的实验中出现问题,可以参阅“用脚本创建Quartus工程”,自动地创建工程。 |

编译错误信息

点击Processing ➤ Start ➤ Start Analysis & Synthesis菜单项或工具栏相应按钮,使用Quartus软件内嵌的分析综合工具Analysis & Synthesis对设计进行逻辑综合。如果综合通过,任务流程区中Analysis & Synthesis步骤前面会显示绿色的勾;如果有语法错误,会显示红色的叉,同时在信息显示区会显示错误信息。

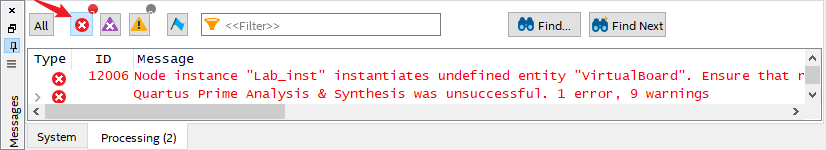

查找错误时,应从第一个错误信息看起,因为后面的错误有可能是由前面的错误引起的。应点击Error标签(红叉),翻到第一个错误信息,如图 3。

“Error (12006): Node instance "Lab_inst" instantiates undefined entity "VirtualBoard". ”这个错误信息是说编译器没找到“VirtualBoard”这个模块。

| 很多初学者不习惯阅读错误信息,实际上学会读懂错误信息是很有用的。可以点鼠标右键将错误信息复制下来,百度看看过来人怎么说,慢慢地就能读懂了。或参阅本项目的常见编译错误。 |

添加模块

设计输入

输入HDL设计代码

前面的综合虽然没有报错,但实际上VirtualBoard模块并没有设计内容。在编辑器中打开VirtualBoard.sv文件,如例 1所示,可以看到该模块只有端口定义。

`default_nettype none

module VirtualBoard (

input wire CLOCK, // 10 MHz Input Clock

input wire [19:0] PB, // 20 Push Buttons, logical 1 when pressed

input wire [35:0] S, // 36 Switches

output logic [35:0] L, // 36 LEDs, drive logical 1 to light up

output logic [7:0] SD7, // 8 common anode Seven-segment Display

output logic [7:0] SD6,

output logic [7:0] SD5,

output logic [7:0] SD4,

output logic [7:0] SD3,

output logic [7:0] SD2,

output logic [7:0] SD1,

output logic [7:0] SD0

);

endmodule例 1的VHDL版本(点击此行展开)

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_unsigned.ALL;

ENTITY VirtualBoard IS

PORT (

CLOCK:in std_logic; -- 10MHz Input Clock

PB: in std_logic_vector(19 downto 0); -- 20 Push buttons, logical 1 when pressed

S: in std_logic_vector(35 downto 0); -- 36 Switches

L: out std_logic_vector(35 downto 0); -- 36 LEDs, drive logical 1 to light up

SD7:out std_logic_vector(7 downto 0); -- 8 common anode Seven-segment Display

SD6:out std_logic_vector(7 downto 0);

SD5:out std_logic_vector(7 downto 0);

SD4:out std_logic_vector(7 downto 0);

SD3:out std_logic_vector(7 downto 0);

SD2:out std_logic_vector(7 downto 0);

SD1:out std_logic_vector(7 downto 0);

SD0:out std_logic_vector(7 downto 0));

END VirtualBoard;

ARCHITECTURE behav_VB OF VirtualBoard IS

BEGIN

END behav_VB;这个VirtualBoard模块可以想象成一个实验板,有1个时钟输入CLOCK, 20个按键PB,36个拨动开关S,36个指示灯L,8个七段数码管SD0~SD7。该模块命名为“VirtualBoard”的含义是“虚拟实验板”,在后面验证时我们会看到,“虚拟实验板”模块与实验调试软件的“虚拟面板”是相互对应的。

下面给VirtualBoard模块添加设计代码。首先用8个拨动开关S7~S0直接驱动七段数码管SD0的8个段,将下面的代码添加到例 1的 endmodule 之前。

//开关7~0直接驱动数码管SD0的各个段

assign SD0 = S[7:0];

//开关11~8驱动指示灯L11~8的亮灭

(1)

//按键PB0驱动指示灯L18

assign L[18] = PB[0];| 1 | 在这里添加Verilog HDL的assign赋值语句,实现S11~S8控制L11~L8的亮灭。 |

例 2的VHDL版本(点击此行展开)

--开关7~0直接驱动数码管SD0的各个段

SD0 <= S(7 downto 0);

--开关11~8驱动指示灯L11~8的亮灭

(1)

--按键PB0驱动指示灯L18

L(18) <= PB(0);| 1 | 在这里添加VHDL的赋值语句,实现S11~S8控制L11~L8的亮灭。 |

在以后的实验中,自己的设计也都是写在VirtualBoard模块中;前面使用LabProject中的LabBoard_TOP等文件建立的工程框架不需要修改。

编译整个工程

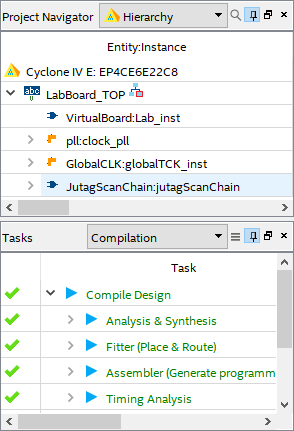

点击Processing ➤ Start Compilation菜单项或工具栏相应按钮,对设计进行全编译。编译成功后,Tasks任务流程区的各个步骤前显示绿色的勾,Project Navigator工程导航区中显示出模块间的层次结构,如图 4。

在output文件夹下找到生成的“xxx.rbf”文件,其中xxx是在建立工程时输入的工程名称;这个文件在验证时要用。

| 有的时候Analysis & Synthesis和Fitter都通过了,但是Assembler或Timing Analysis没有通过,此时只要在任务流程区双击该步骤重做一次,一般都能成功。 |