实现整数运算指令

实验原理

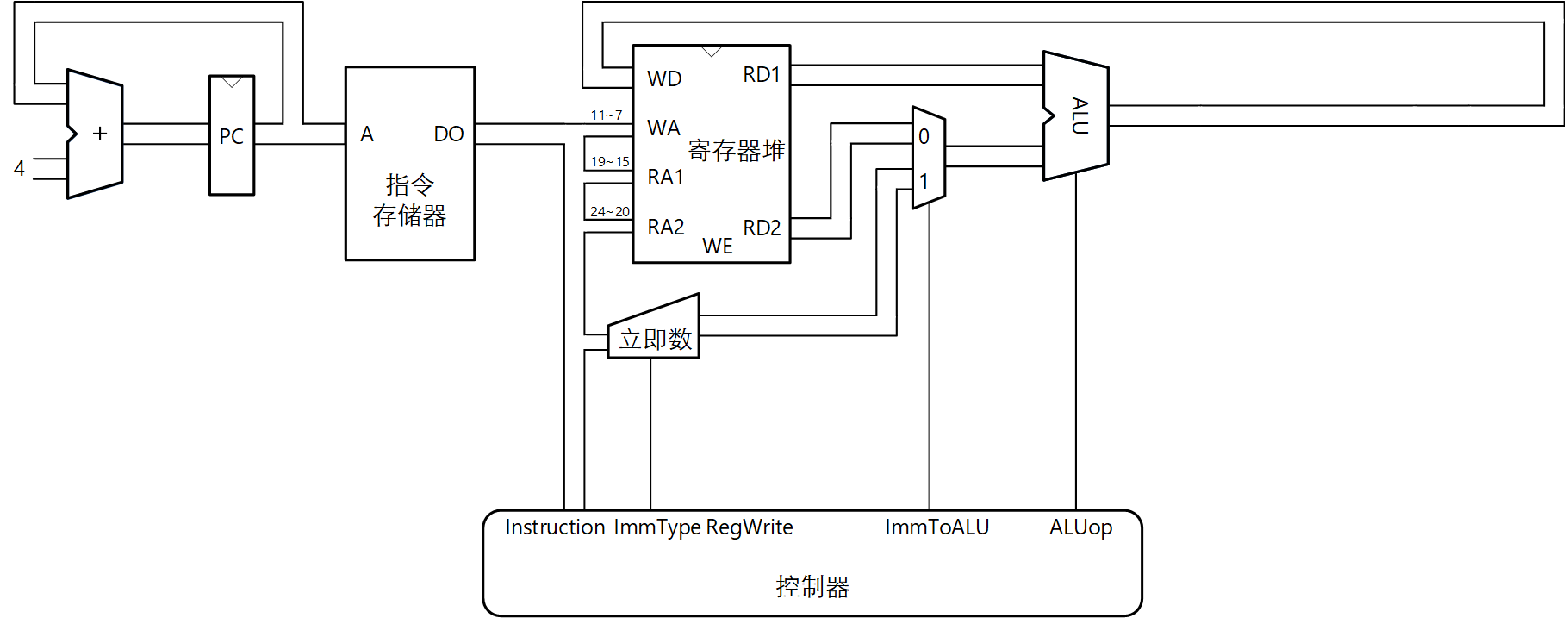

前面ADDI指令的参考设计没有ALU模块,只能进行加法运算,为了实现更多的I型运算指令,需要添加ALU模块;参考设计只能是rs1加立即数,而R型运算指令和I型运算指令的区别在于第二个运算数的来源不同,I型指令是立即数,R型指令是寄存器,所以增加一个多路器进行选择,数据通路如图 1。

实验步骤

1. 用HDL设计实现数据通路

(1)增加ALU模块

将前面实验中自己设计的ALU模块添加到工程中。为便于考核,ALU运算功能的控制请按表 1设计。不要求实现SLTI/SLTIU(小于置1)指令,ALU设计可忽略该指令的需要。

ALUop |

功能描述 |

0001 |

加法 |

0010 |

减法 |

0011 |

按位逻辑与 |

0100 |

按位逻辑或 |

0101 |

按位逻辑异或 |

0110 |

算术右移 |

0111 |

逻辑左移 |

1000 |

逻辑右移 |

【提示】设计时需考虑移位运算的移位位数最多31位。

(2)连接CPU数据通路

实例化ALU模块,添加多路器;根据Controller模块的修改(见下)增加ALUop端口连接,连接增加的控制信号。

2. 设计控制逻辑

修改Controller模块,增加ImmToALU控制信号, 产生ALUop控制信号。注意少数指令的Funct3相同,由Funct7区分,如逻辑右移指令和算术右移指令,加法和减法指令。

R型指令与立即数无关,理论上立即数类型以及生成的立即数对指令结果没有影响。由于实验平台根据控制信号绘制动态信息流显示,为避免显示错误的信息流,建议R型指令的ImmType为0,并且生成的立即数为0。

3. 增加调试支持代码

验证任务提供了设计好的虚拟面板,和ADDI指令的参考设计相比,增加ImmToALU、ALUop等观察信号和RD2等观察数据。需要做的是在代码中增加相应的调试支持,注意序号和位宽一定要和虚拟面板一致,下面给出与虚拟面板对应的WS和WD示例。

always_comb begin

ws.WS3[3:0] = cALUop;

ws.WS2[4:0] = cImm_type;

ws.WS1 = cImmToALU;

ws.WS0 = cRegWrite;

End

always_comb begin

wd.WD9[31:0] = immData;

wd.WD8[31:0] = regReadData2;

wd.WD7[31:0] = regReadData1;

wd.WD6[4:0] = ra2;

wd.WD5[4:0] = ra1;

wd.WD4[31:0] = regWriteData;

wd.WD3[4:0] = wa;

wd.WD2[31:0] = instruction;

wd.WD1[31:0] = pc;

wd.WD0[31:0] = nextPC;

end

4. 在实验平台验证设计

根据ALU所实现的运算功能,执行相应的Ⅰ型和R型运算指令,并检查指令执行结果。

(1)Ⅰ型运算指令的参考测试程序

addi x0, x0, 0

addi x18, x0, 0x666

addi x18, x18, 0

andi x19, x18, 0x555

addi x19, x19, 0

ori x20, x18, 0x333

addi x20, x20, 0

xori x21, x18, -1

addi x21, x21, 0

slli x5, x18, 21

addi x5, x5, 0

srai x6, x18, 10

addi x6, x6, 0

srli x7, x18, 10

addi x7, x7, 0

srai x6, x5, 12

addi x6, x6, 0

srli x7, x5, 12

addi x7, x7, 0

(2)R型运算指令的参考测试程序

addi x18, x0, 0x666

addi x17, x0, 0x555

and x19, x18, x17

addi x19, x19, 0

or x20, x18, x17

addi x20, x20, 0

xor x21, x18, x17

addi x21, x21, 0

add x22, x18, x17

addi x22, x22, 0

sub x23, x18, x17

addi x23, x23, 0

addi x28, x0, 21

sll x5, x18, x28

addi x5, x5, 0

addi x28, x0, 10

sra x6, x18, x28

addi x6, x6, 0

srl x7, x18, x28

addi x7, x7, 0

addi x28, x0, 12

sra x6, x5, x28

addi x6, x6, 0

srl x7, x5, x28

addi x7, x7, 0

(3)编写自己的测试程序

编写一个综合Ⅰ型和R型运算指令的测试程序,验证自己的设计。根据指导教师的要求,提交验证记录。