实现分支指令

实验原理

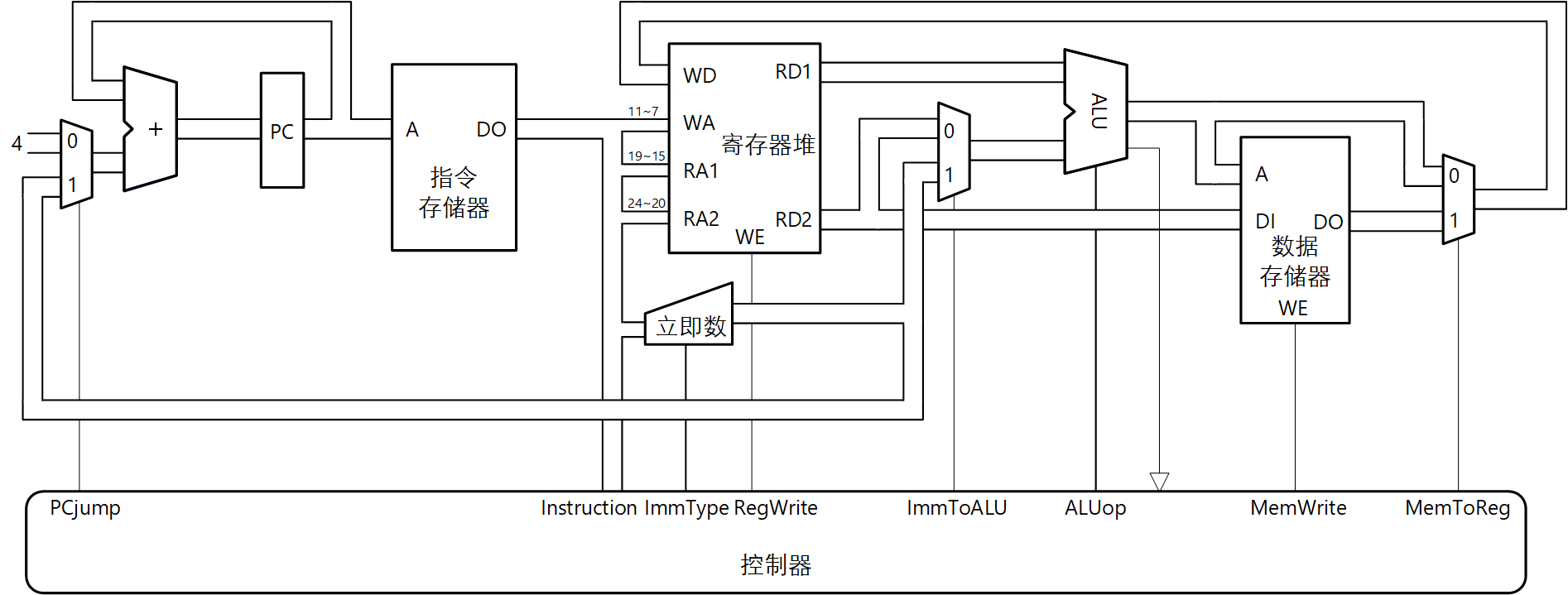

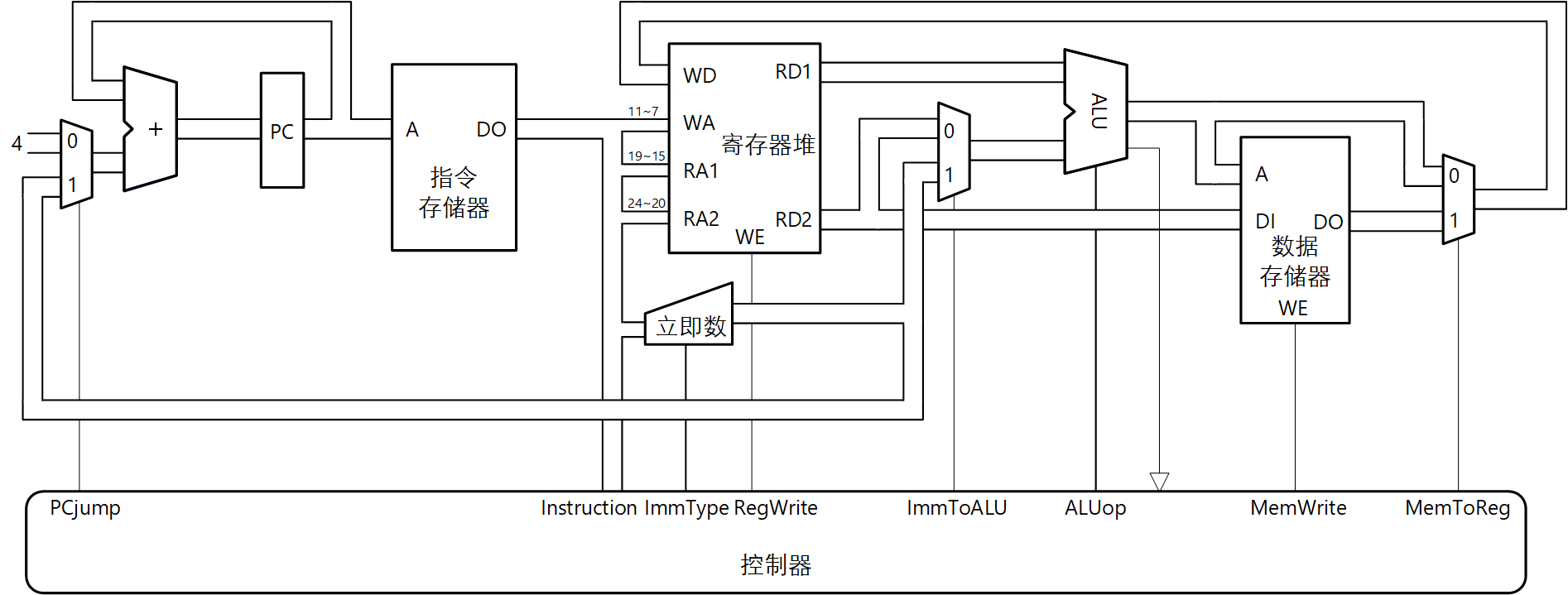

分支指令包括beq、bne、blt、bge以及bltu、bgeu指令。数据通路如图 1。

图 1. 支持分支指令的数据通路

实验步骤

2. 实现数据通路

(1)修改ImmGen模块

增加B型立即数的生成。注意B型立即数实际是13位立即数,最低位需要补0。

(2)修改CPU模块

添加多路器,根据图 1连接数据通路各个部件;连接增加的控制信号。

分支指令包括beq、bne、blt、bge以及bltu、bgeu指令。数据通路如图 1。

(1)修改ImmGen模块

增加B型立即数的生成。注意B型立即数实际是13位立即数,最低位需要补0。

(2)修改CPU模块

添加多路器,根据图 1连接数据通路各个部件;连接增加的控制信号。