寄存器堆实验

参考设计

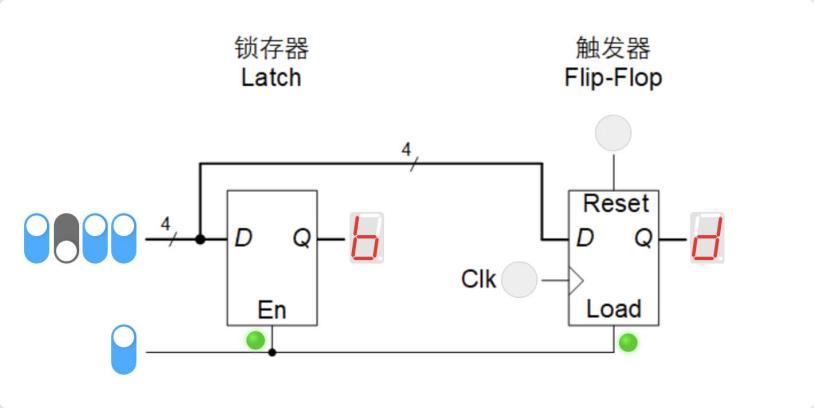

实验材料中给出了触发器模块和锁存器模块的HDL代码,并且在VirtualBoard模块中实例化。图 1是虚拟面板的运行效果,通过验证体会触发器和锁存器的区别。

实验内容和要求

CPU内部通常包含若干个通用寄存器(Genral Register),以暂存参加运算的数据和中间结果。这些寄存器的集合就称为寄存器组(Register Set)、寄存器文件(Register File)或寄存器堆。为方便访问其中的寄存器,对寄存器堆中的寄存器进行统一编码,称为寄存器号(Index)或者寄存器地址。单端口是指读出和写入共用同一组地址或数据端口,所以读出和写入不能同时进行,通常应用于多周期的数据通路;而三端口的读、写端口各自独立,在一个周期中既可以读出也可以写入,通常应用于单周期数据通路。本实验完成三端口寄存器堆。

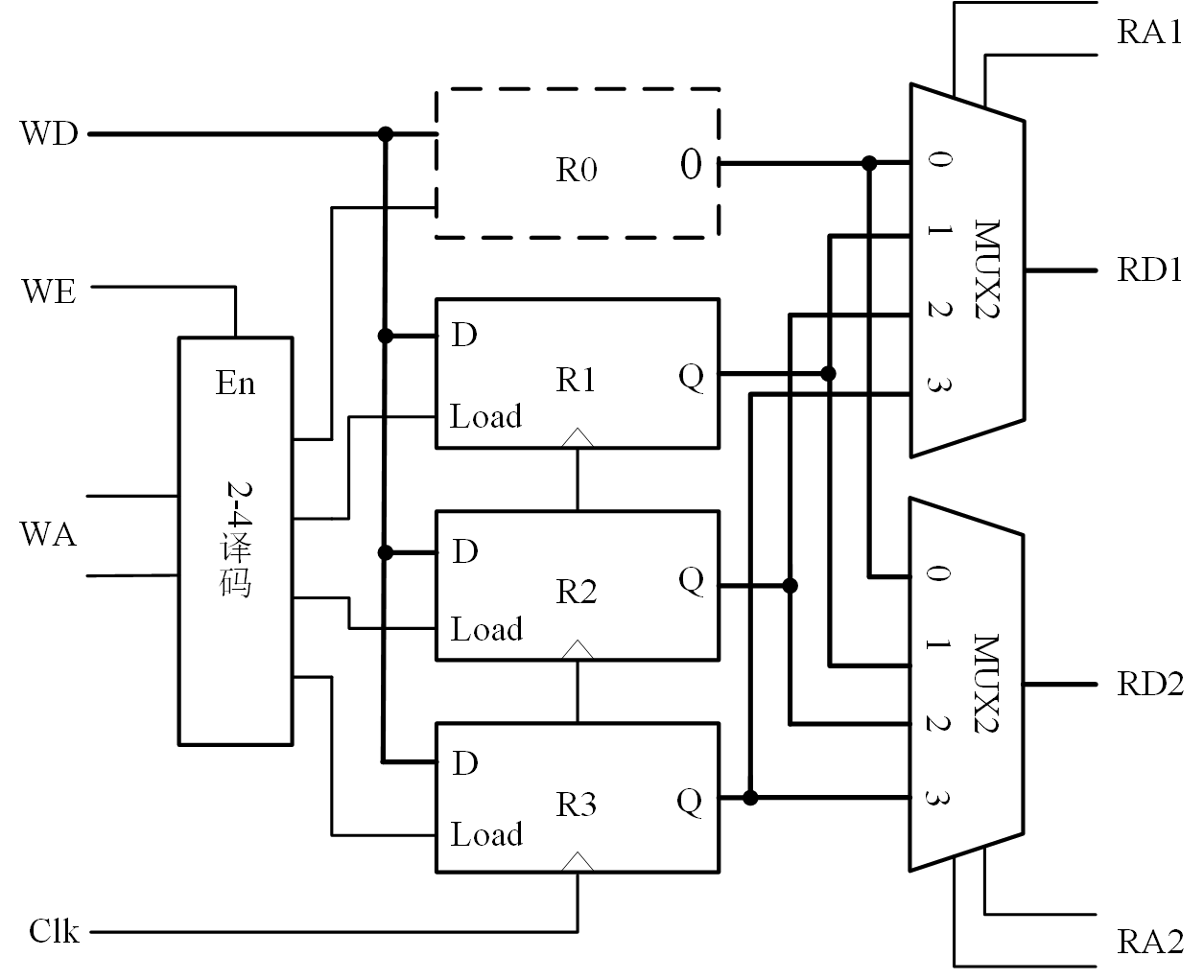

图 2是具有2个读端口和1个写端口的寄存器堆的电路结构。其中RA表示读端口地址(Read Address),RD表示读端口数据(Read Data);WA表示写端口地址(Write Address),WD表示写端口数据(Write Data);WE是写使能(Write Enable),其作用与图 1触发器的Load相同。理解图 2结构并用HDL设计该寄存器堆,要求2-4译码器和4选1多路器均写成独立模块,寄存器使用参考设计的寄存器模块实例化。此外还有一个特殊的要求,R0寄存器读出值恒为0,也可理解为R0不可写入。

|

关于写时读

从某一个读端口读出某一个寄存器的内容时,如果写端口同时也在向这个寄存器写入新数据,那么读出的是以前的旧数据还是正在写入的新数据?这两种方案对后面CPU实验流水线数据冲突的解决方案有影响。我们采用的方案是读出之前存入寄存器的旧数据。在一些教材上也有采用读出新数据的方案,其具体实现方法有两种。一种是“旁路”,写寄存器的同时将要写入的数据直接送到读端口,这种方法需要确保读出时数据是稳定的;另一种方法是在一个周期的前半个周期写入,后半个周期从已经写入的寄存器中读出,这种方法其实是延长了一个周期的长度。 |