计数器与分频器实验

实验内容和要求

参考设计

流水灯实验中用按键手动产生时钟信号,本实验使用系统的连续时钟,使流水灯能自动移动。由于系统时钟的频率比较高,进入到VirtualBoard模块的CLOCK信号的频率是10MHz;如果直接用它作为移位寄存器的时钟,人的肉眼将无法分辨出LED灯的移动。所以需要设计一个分频器将时钟频率降下来。

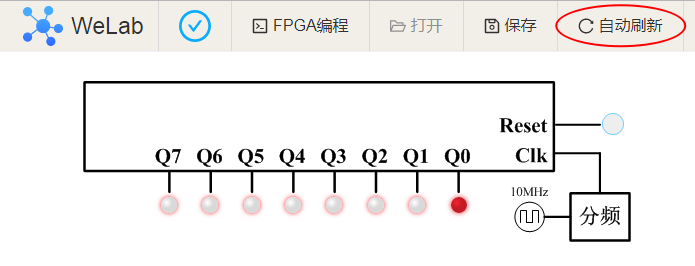

实验材料中给出了一个二进制计数器的设计,认真阅读并理解HDL代码,计算出送给移位寄存器的clk信号的周期(频率的倒数);编译后下载到实验板上,观察流水灯的自动移动。注意需开启虚拟面板的自动刷新,如图 1所示。远程实验系统默认的自动刷新时间间隔为1000毫秒。

思考为什么观察到的流水灯移动会跳跃,如何才能观察到LED灯的匀速移动(提示:需根据clk信号的周期恰当设置刷新间隔)。

实验任务1

用HDL设计一个分频器,对10MHz输入时钟进行分频,分频后的时钟频率为1Hz。使用分频后的时钟作为移位寄存器的时钟,使LED灯每隔1秒移动一位。运行效果如图 2。

分频器要求写成独立模块,端口声明如下。

module ClockDivider #(parameter RATIO = 8) ( input wire ClkIn,Reset, output reg ClkOut );

其中参数RATIO用来声明分频数。

实验任务2

用ModelSim仿真参考设计。关于ModelSim的用法请阅读实验教程《ModelSim仿真入门》,下面针对本实验做几点说明。

(1)Testbench在实验材料中已经提供,应读懂。本实验只做功能仿真,被仿真的设计模块是VirtualBoard。

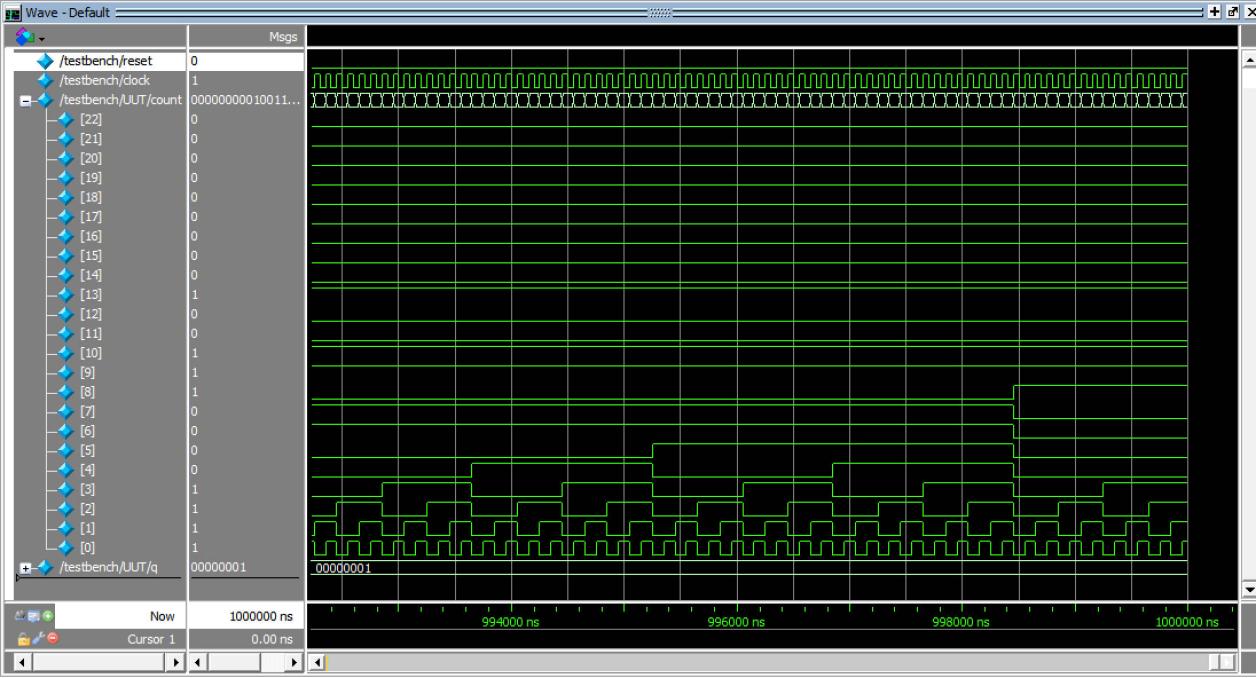

(2)需要手动将count和q添加到波形窗口,重新启动仿真后的波形如图 3。

从波形上看移位寄存器的输出q(图中最后一行)一直是00000001没有变化,也就是复位的初值。这是因为仿真的时间不够长,计数器count还没有溢出。可以修改testbench,延长停止仿真前的时长;或者将设计代码中的“assign clk = count[22];”改为较小的分频数以便能观察到q的变化。